RM0016 16-bit general purpose timers (TIM2, TIM3, TIM5)

Doc ID 14587 Rev 8 233/449

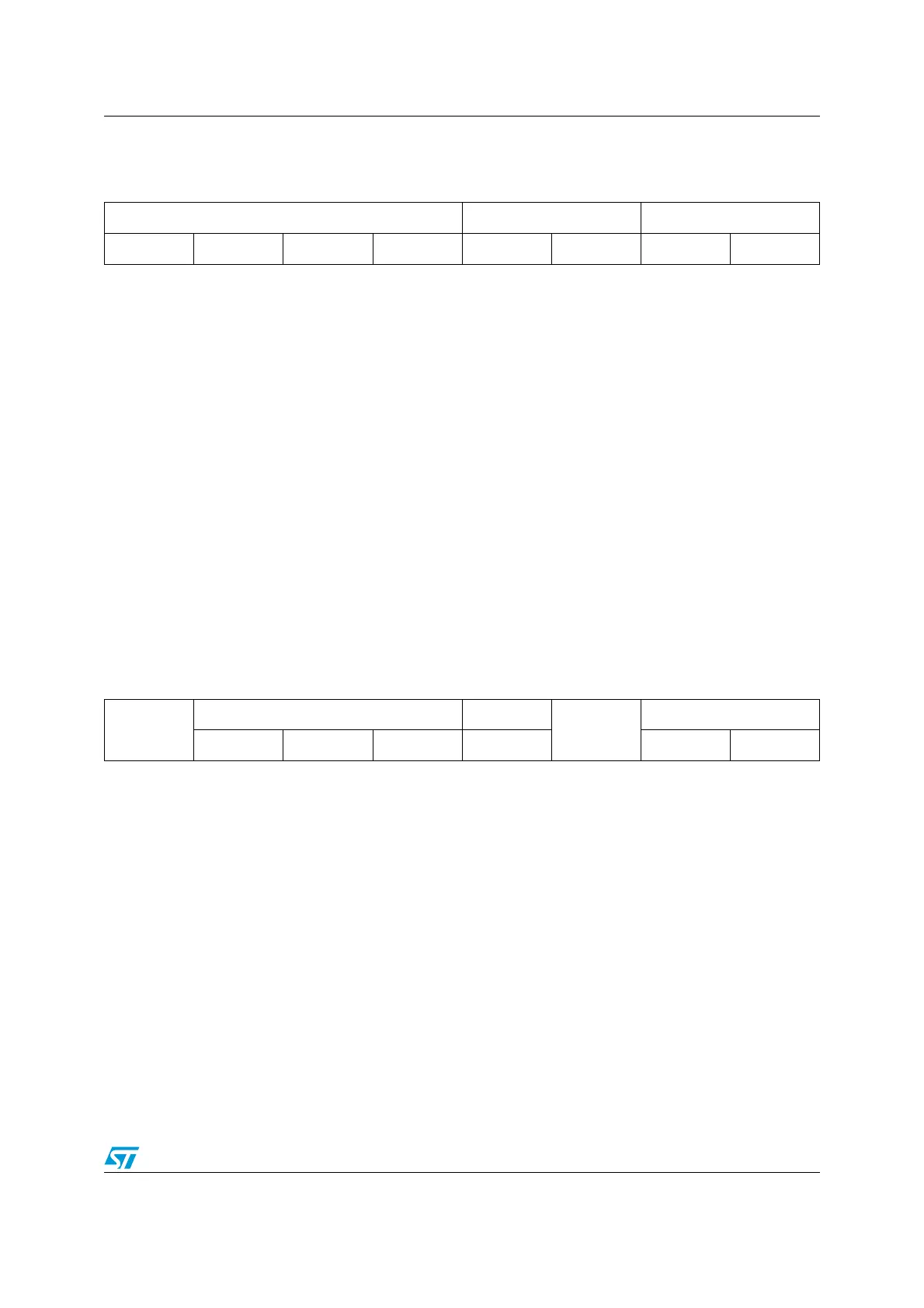

Channel configured in input

18.6.10 Capture/compare mode register 3 (TIMx_CCMR3)

Refer to Capture/compare mode register 1 (TIM1_CCMR1) on page 195 for details on using

these bits.

Address offset: 0x07 or 0x09 (TIM2), 0x09 (TIM5); for TIM2 address see Section

Reset value: 0x00

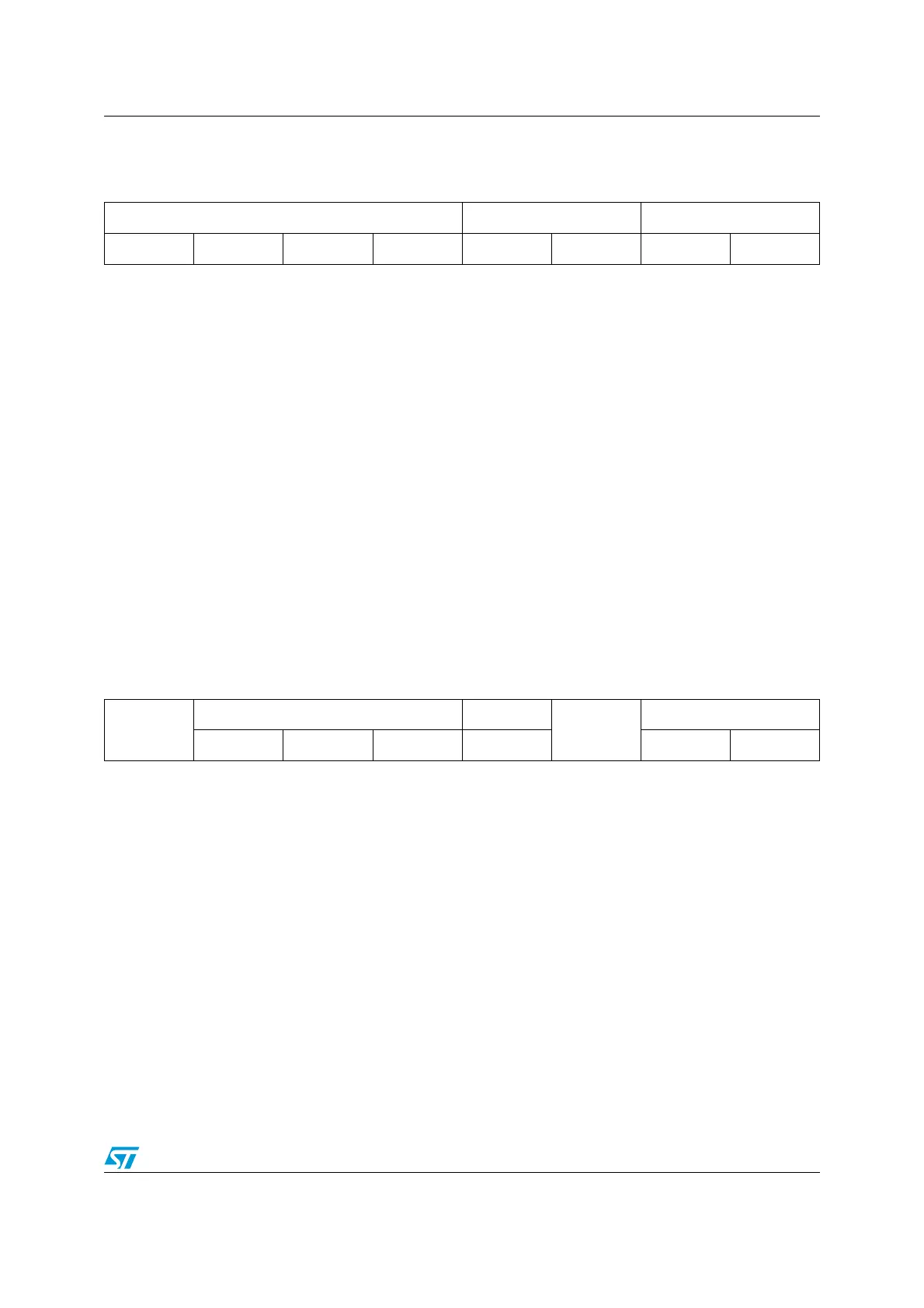

Channel configured in output

Note: This register is not available in TIM3.

76543210

IC2F[3:0] IC2PSC[1:0] CC2S[1:0]

rw rw rw rw rw

rw

rw rw

Bits 7:4 IC2F[3:0]: Input capture 2 filter

Bits 3:2 IC2PCS[1:0]: Input capture 2 prescaler

Bits 1:0 CC2S[1:0]: Capture/compare 2 selection

This bitfield defines the direction of the channel (input/output) as well as the used input.

00: CC2 channel is configured as output

01: CC2 channel is configured as input, IC2 is mapped on TI2FP2

10: CC2 channel is configured as input, IC2 is mapped on TI1FP2

11: Reserved

Note: CC2S bits are writable only when the channel is off (CC2E = 0 in TIMx_CCER1).

76543210

Reserved

OC3M[2:0] OC3PE

Reserved

CC3S[1:0]

rw rw rw rw rw rw

Bit 7 Reserved

Bits 6:4 OC3M[2:0]: Output compare 3 mode

Bit 3 OC3PE: Output compare 3 preload enable

Bit 2 Reserved

Bits 1:0 CC3S[1:0]: Capture/compare 3 selection

This bitfield defines the direction of the channel (input/output) as well as the used input.

00: CC3 channel is configured as output

01: CC3 channel is configured as input, IC3 is mapped on TI3FP3

10: Reserved

11: Reserved

Note: CC3S bits are writable only when the channel is off (CC3E = 0 in TIMx_CCER2).

Loading...

Loading...