RM0016 Controller area network (beCAN)

Doc ID 14587 Rev 8 385/449

23.11 beCAN registers

23.11.1 CAN master control register (CAN_MCR)

Address offset: 0x00

Reset value: 0x02

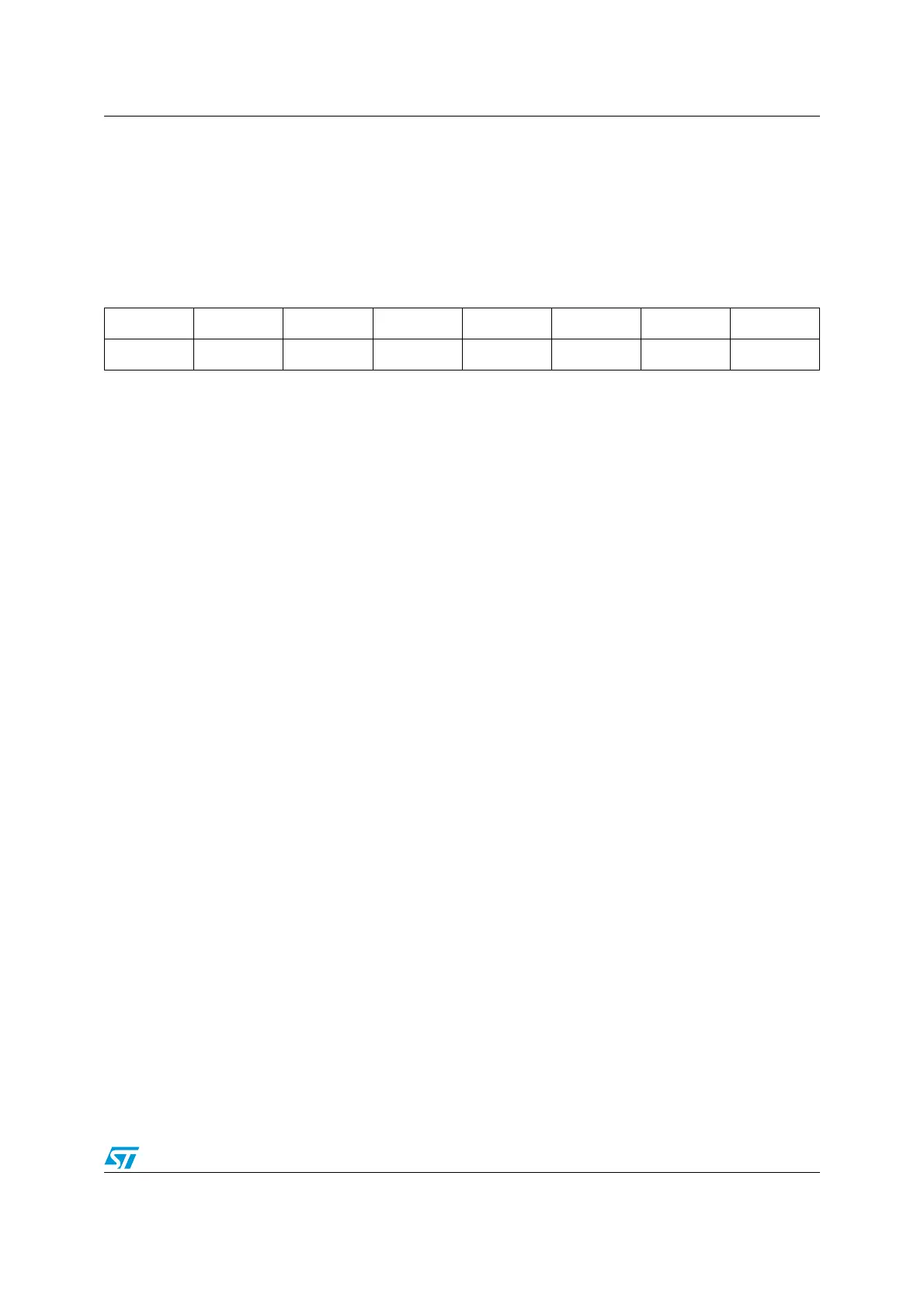

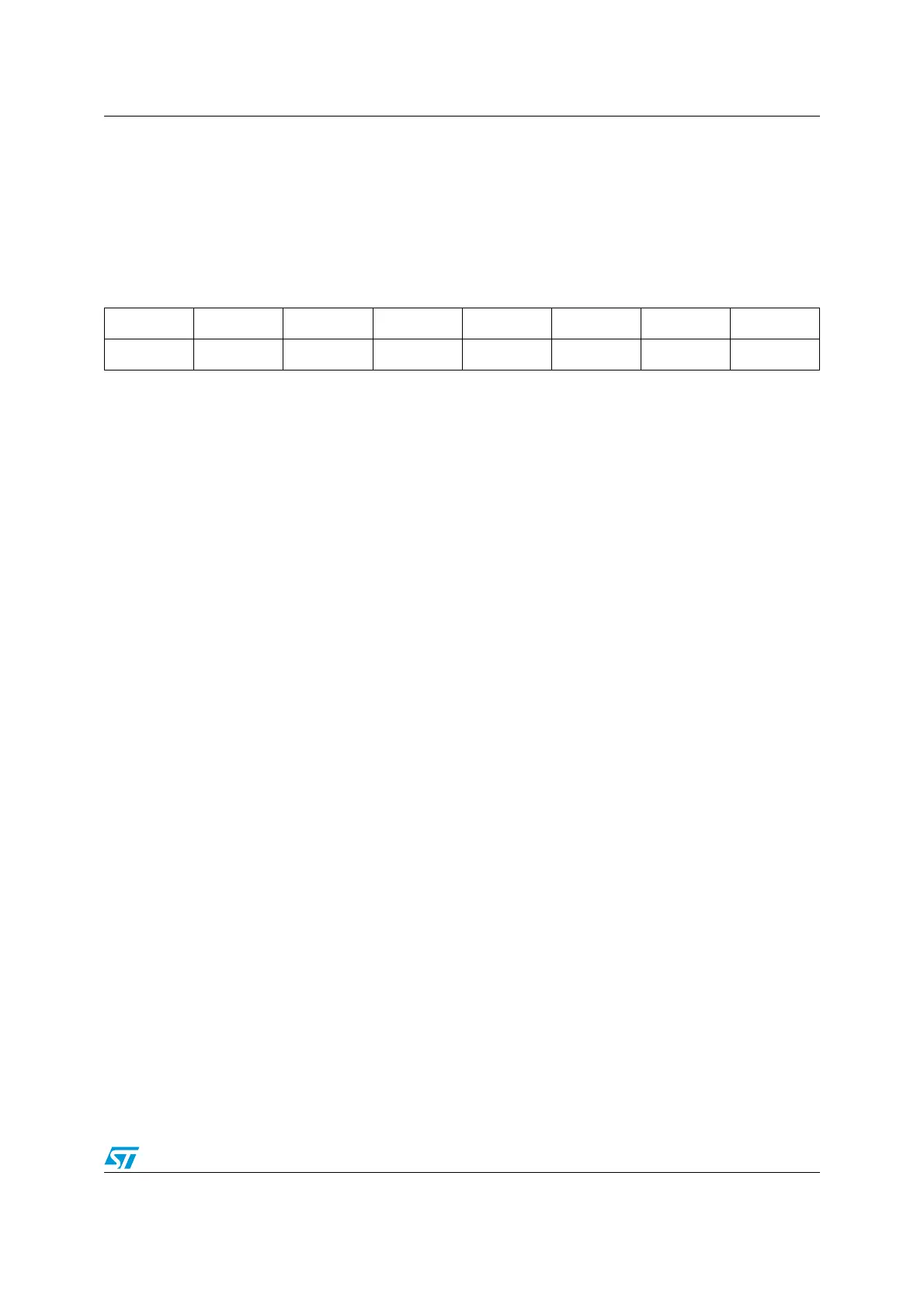

76543210

TTCM ABOM AWUM NART RFLM TXFP SLEEP INRQ

rw rw rw rw rw rw rw rw

Bit 7 TTCM Time Triggered Communication Mode

0: Time Triggered Communication mode disabled.

1: Time Triggered Communication mode enabled

Note: For more information on Time Triggered Communication mode, please refer to Section 23.4.4:

Time triggered communication mode.

Bit 6 ABOM Automatic Bus-Off Management

This bit controls the behavior of the CAN hardware on leaving the Bus-Off state.

0: The Bus-Off state is exited on software request.

Refer to Section 23.6.5: Error management, Bus-Off recovery.

1: The Bus-Off state is exited automatically by hardware once 128 x 11 recessive bits have been

monitored.

Note: For detailed information on the Bus-Off state please refer to Section 23.6.5: Error management.

Bit 5 AWUM Automatic wakeup Mode

This bit controls the behavior of the CAN hardware when a message is received in Sleep mode.

0: The sleep mode is exited on software request by clearing the SLEEP bit in the CAN_MCR

register.

1: The sleep mode is exited automatically by hardware when a CAN message is detected. In this

case, the SLEEP bit of the CAN_MCR register and the SLAK bit of the CAN_MSR register are

cleared by hardware, while the WKUI bit of the CAN_MSR register is set. If the CAN bus is active

when the Sleep automatic wakeup request occurs,it does not enter Sleep mode.

The AWUM and the SLEEP bits must be set simultaneously.

Bit 4 NART No Automatic Retransmission

0: The CAN hardware will automatically retransmit the message until it has been successfully

transmitted according to the CAN standard.

1: A message will be transmitted only once, independently of the transmission result (successful,

error or arbitration lost).

Bit 3 RFLM Receive FIFO Locked Mode

0: Receive FIFO not locked on overrun. Once a receive FIFO is full the next incoming message will

overwrite the previous one.

1: Receive FIFO locked against overrun. Once a receive FIFO is full the next incoming message will

be discarded.

Bit 2 TXFP Transmit FIFO Priority

This bit controls the transmission order when several mailboxes are pending at the same time.

0: Priority driven by the identifier of the message

1: Priority driven by the request order (chronologically)

Loading...

Loading...