RM0016 16-bit advanced control timer (TIM1)

Doc ID 14587 Rev 8 185/449

17.7 TIM1 registers

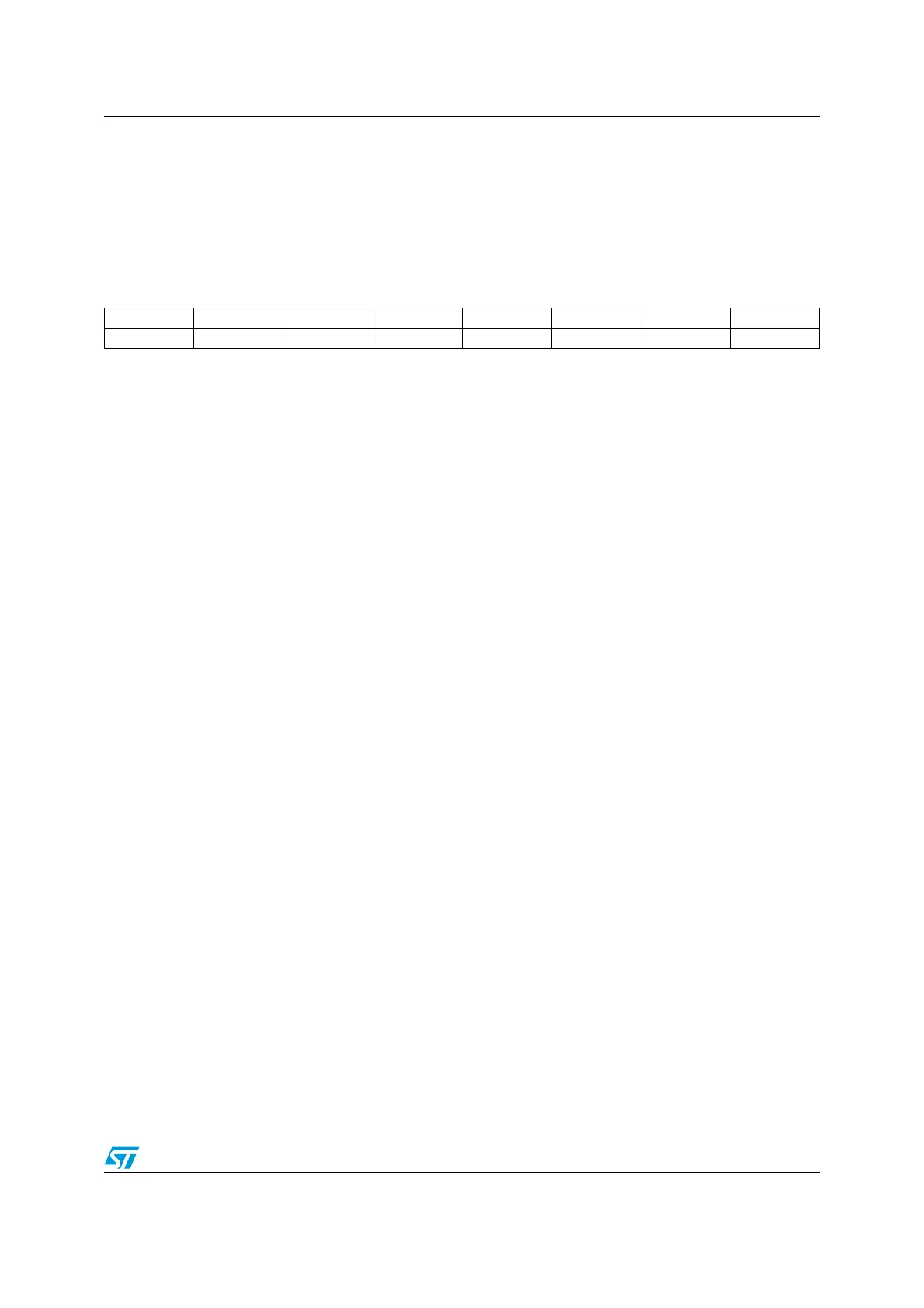

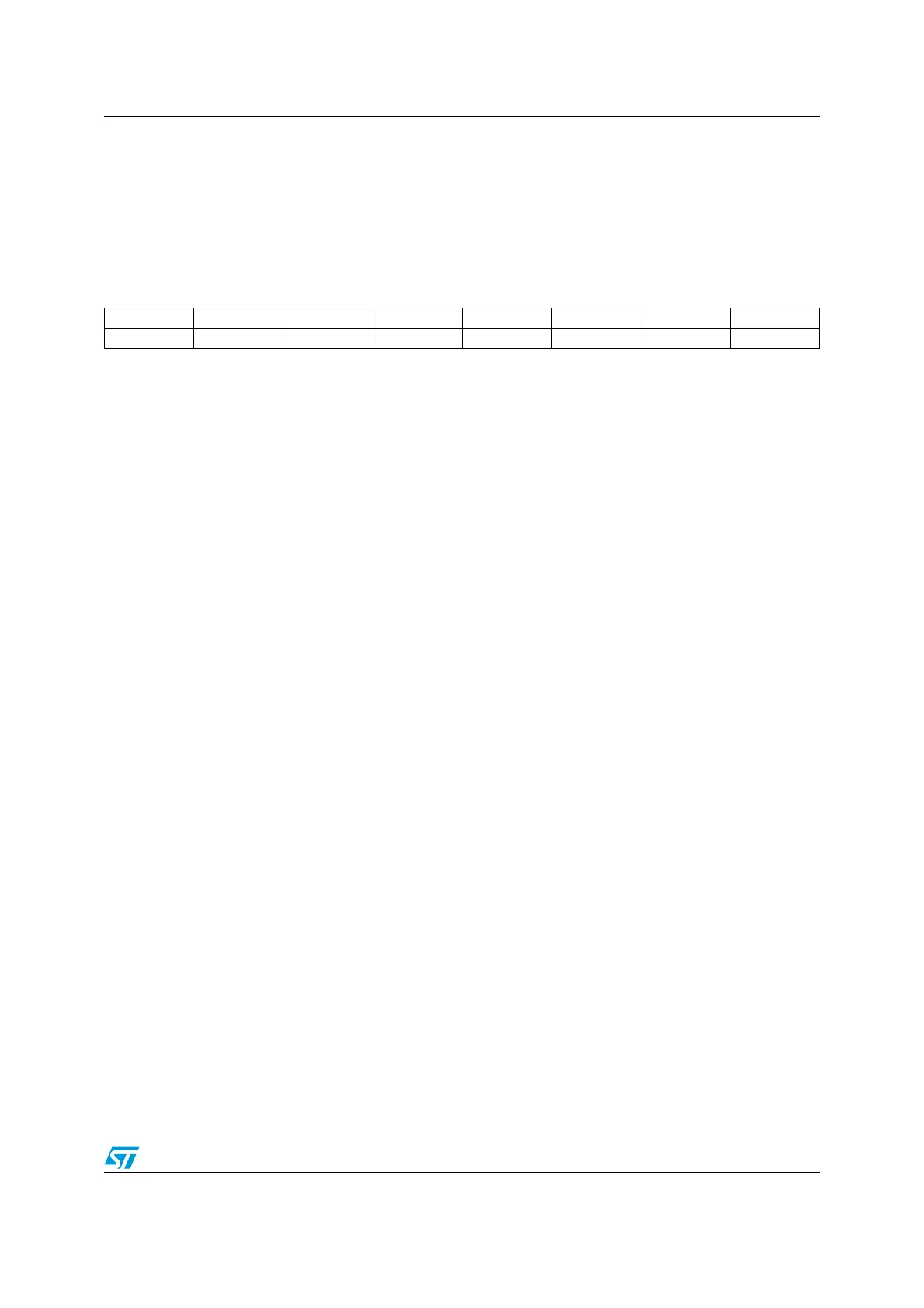

17.7.1 Control register 1 (TIM1_CR1)

Address offset: 0x00

Reset value: 0x00

76543210

ARPE CMS[1:0] DIR OPM URS UDIS CEN

rw rw rw rw rw rw rw rw

Bit 7 ARPE: Auto-reload preload enable

0: TIM1_ARR register is not buffered through a preload register. It can be written directly

1: TIM1_ARR register is buffered through a preload register

Bits 6:5 CMS[1:0]: Center-aligned mode selection

00: Edge-aligned mode. The counter counts up or down depending on the direction bit (DIR).

01: Center-aligned mode 1. The counter counts up and down alternately. Output compare interrupt

flags of channels configured in output (CCiS = 00 in TIM1_CCMRi registers) are set only when the

counter is counting down.

10: Center-aligned mode 2. The counter counts up and down alternately. Output compare interrupt

flags of channels configured in output (CCiS = 00 in CCMRi registers) are set only when the counter

is counting up.

11: Center-aligned mode 3. The counter counts up and down alternately. Output compare interrupt

flags of channels configured in output (CCiS = 00 in TIM1_CCMRi registers) are set both when the

counter is counting up and down.

Note: It is not allowed to switch from edge-aligned mode to center-aligned mode while the counter is

enabled (CEN = 1)

Encoder mode (SMS = 001, 010 or 011 in TIM1_SMCR register) must be disabled in center-

aligned mode.

Bit 4 DIR: Direction

0: Counter used as up-counter

1: Counter used as down-counter

Note: This bit is read-only when the timer is configured in center-aligned mode or encoder mode.

Bit 3 OPM: One-pulse mode

0: Counter is not stopped at update event

1: Counter stops counting at the next update event (clearing the CEN bit)

Bit 2 URS: Update request source

0: When enabled by the UDIS bit, the UIF bit is set and an update interrupt request is sent when one

of the following events occurs:

– Registers are updated (counter overflow/underflow)

– UG bit is set by software

– Update event is generated through the clock/trigger controller

1: When enabled by the UDIS bit, the UIF bit is set and an update interrupt request is sent only when

registers are updated (counter overflow/underflow).

Loading...

Loading...