RM0016 Controller area network (beCAN)

Doc ID 14587 Rev 8 395/449

23.11.14 CAN bit timing register 2 (CAN_BTR2)

Address offset: See Table 70.

Reset value: 0x23

This register can only be accessed by the software when the CAN hardware is in

initialization mode.

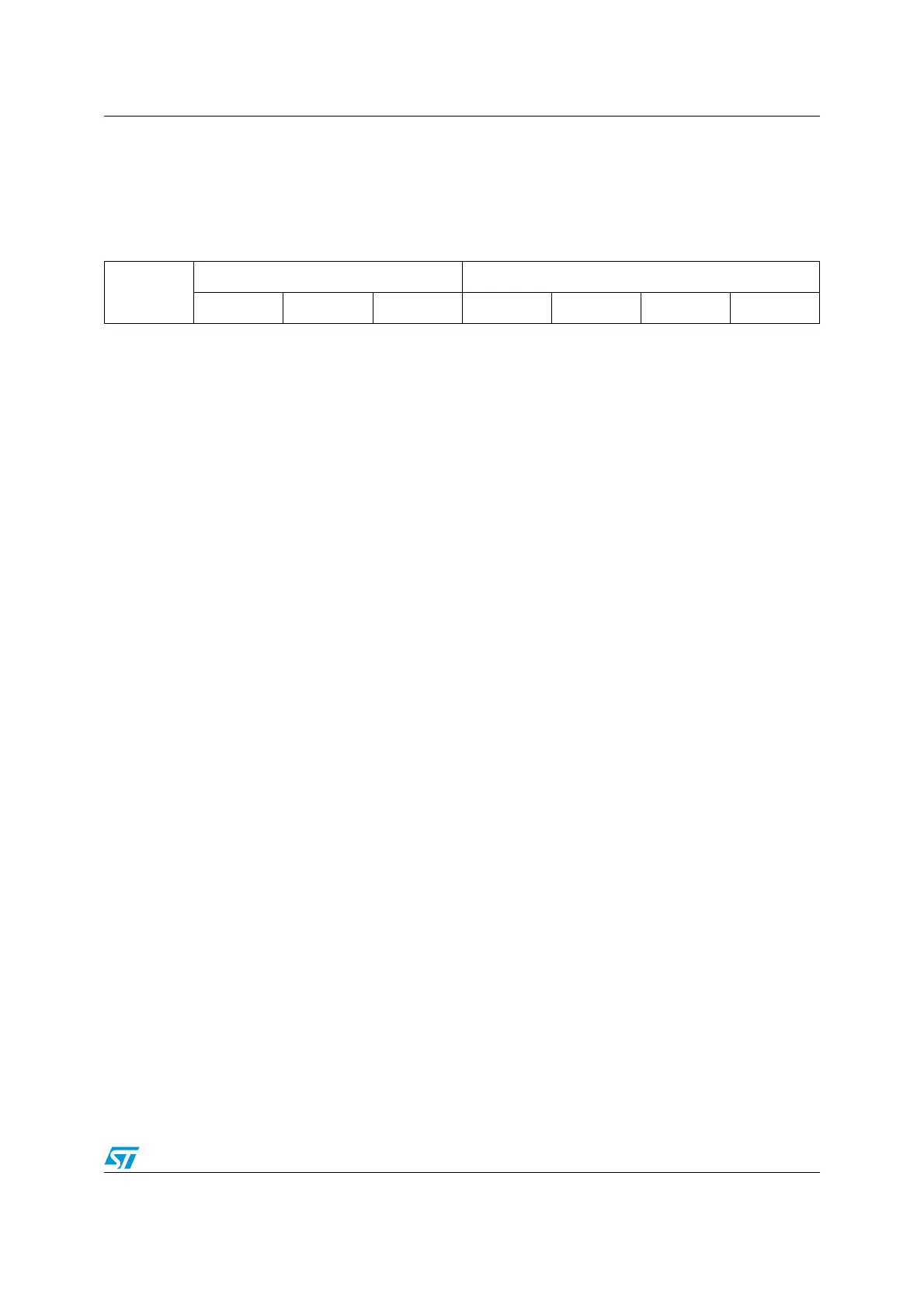

76543210

Reserved

BS2[2:0] BS1[3:0]

rw rw rw rw rw rw rw

Bit 7 Reserved, must be kept cleared.

Bits 6:4 BS2[2:0] Bit Segment 2

These bits define the number of time quanta in Bit Segment 2.

Bit Segment 2 = (BS2+1)

Bits 3:0 BS1[3:0] Bit Segment 1

These bits define the number of time quanta in Bit Segment 1

Bit Segment 1 = (BS1+1)

For more information on bit timing, please refer to Section 23.6.6: Bit timing.

Loading...

Loading...