Analog/digital converter (ADC) RM0016

438/449 Doc ID 14587 Rev 8

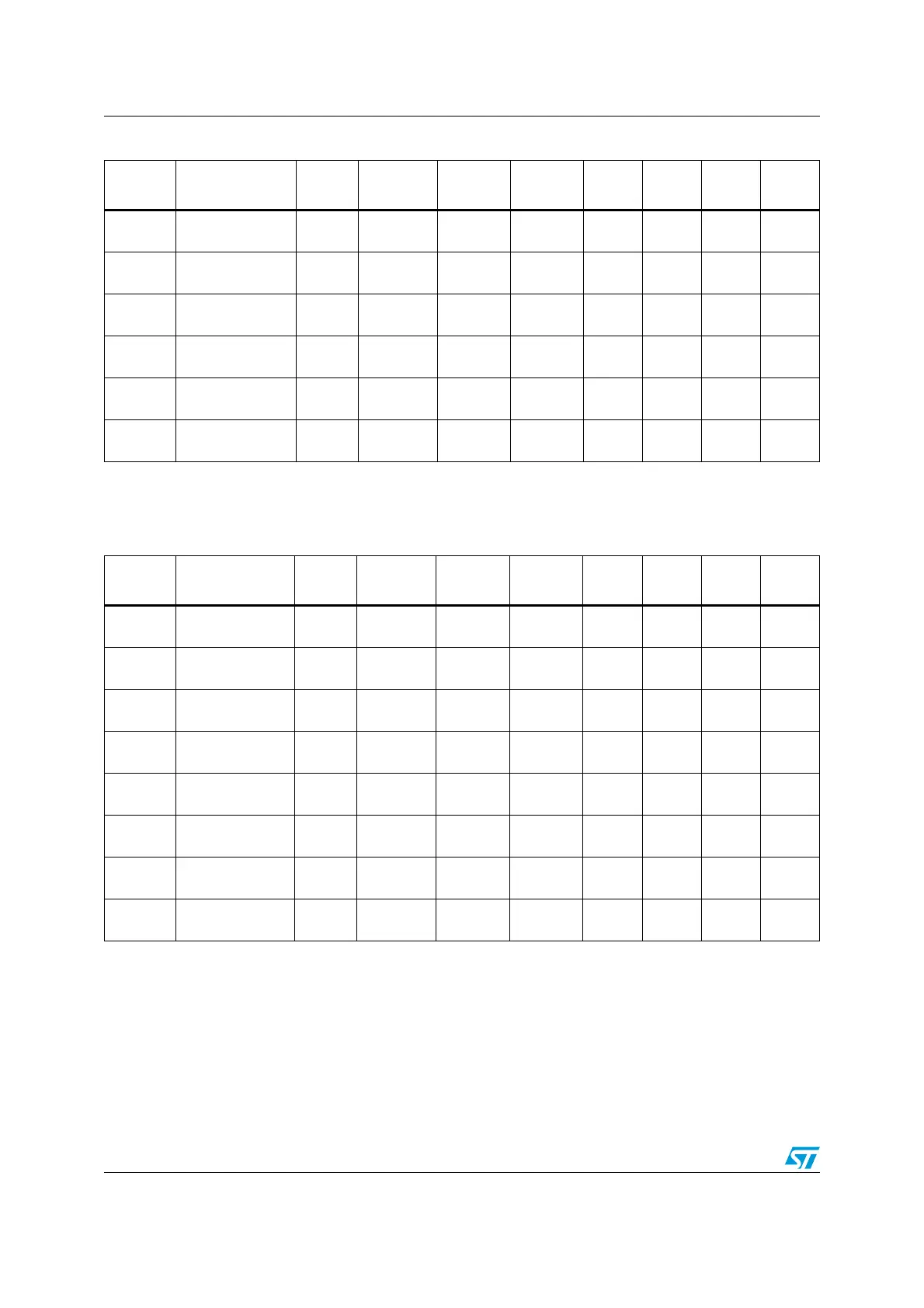

0x2A

ADC1 _LTRH

Reset value

LT9

0

LT8

0

LT7

0

LT6

0

LT5

0

LT4

0

LT3

0

LT2

0

0x2B

ADC1_LTRL

Reset value

-

0

-

0

-

0

-

0

-

0

-

0

LT1

0

LT0

0

0x2C

ADC1 _AWSRH

(2)

Reset value

-

0

-

0

-

0

-

0

-

0

-

0

AWS9

0

AWS8

0

0x2D

ADC1_AWSRL

Reset value

AWS7

0

AWS6

0

AWS5

0

AWS4

0

AWS3

0

AWS2

0

AWS1

0

AWS0

0

0x2E

ADC1 _AWCRH

(2)

Reset value

-

0

-

0

-

0

-

0

-

0

-

0

AWEN9

0

AWEN8

0

0x2F

ADC1_AWCRL

Reset value

AWEN7

0

AWEN6

0

AWEN5

0

AWEN4

0

AWEN3

0

AWEN2

0

AWEN1

0

AWEN0

0

1. This register is reserved in devices with buffer size 8 x 10 bits.

2. This register is reserved in devices without ADC channels 8 and 9.

Table 76. ADC1 register map and reset values (continued)

Address

offset

Register name 7 6 5 4 3 2 1 0

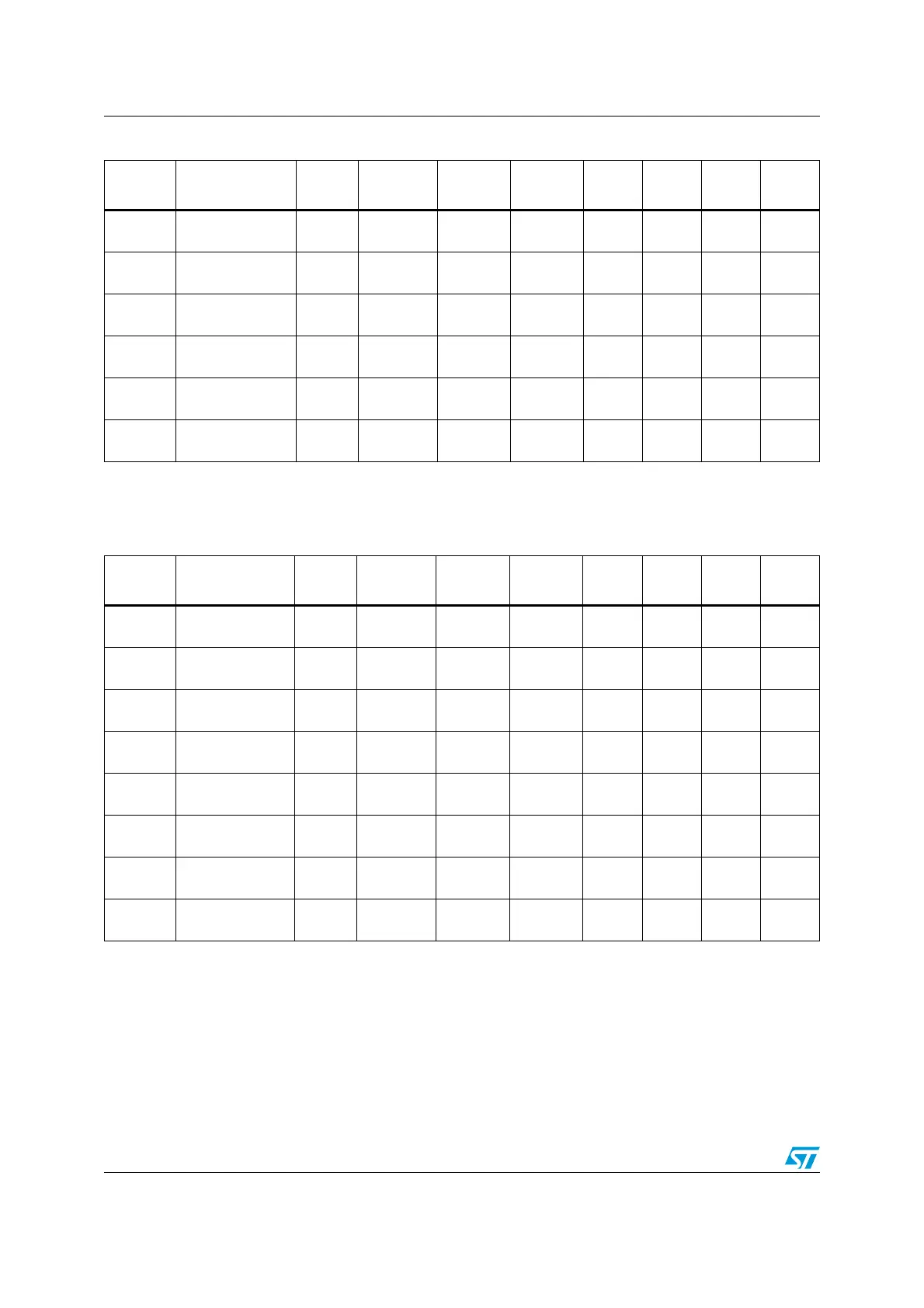

Table 77. ADC2 register map and reset values

Address

offset

Register name 7 6 5 4 3 2 1 0

0x20

ADC2 _CSR

Reset value

EOC

0

AWD

0

EOCIE

0

AWDIE

0

CH3

0

CH2

0

CH1

0

CH0

0

0x21

ADC2_CR1

Reset value

-

0

SPSEL2

0

SPSEL1

0

SPSEL0

0

-

0

-

0

CONT

0

ADON

0

0x22

ADC2_CR2

Reset value

-

0

EXTTRIG

0

EXTSEL1

0

EXTSEL0

0

ALIGN

0

-

0

-

0

-

0

0x23

ADC2_CR3

Reset value

DBUF

0

OVR

0

-

0

-

0

-

0

-

0

-

0

-

0

0x24

ADC2_DRH

Reset value

-

0

-

0

-

0

-

0

-

0

-

0

DATA9

0

DATA8

0

0x25

ADC2_DRL

Reset value

DATA7

0

DATA6

0

DATA5

0

DATA4

0

DATA3

0

DATA2

0

DATA1

0

DATA0

0

0x26

ADC2_TDRH

Reset value

TD15

0

TD14

0

TD13

0

TD12

0

TD11

0

TD10

0

TD9

0

TD8

0

0x27

ADC2_TDRL

Reset value

TD7

0

TD6

0

TD5

0

TD4

0

TD3

0

TD2

0

TD1

0

TD0

0

Loading...

Loading...