RM0016 Clock control (CLK)

Doc ID 14587 Rev 8 93/449

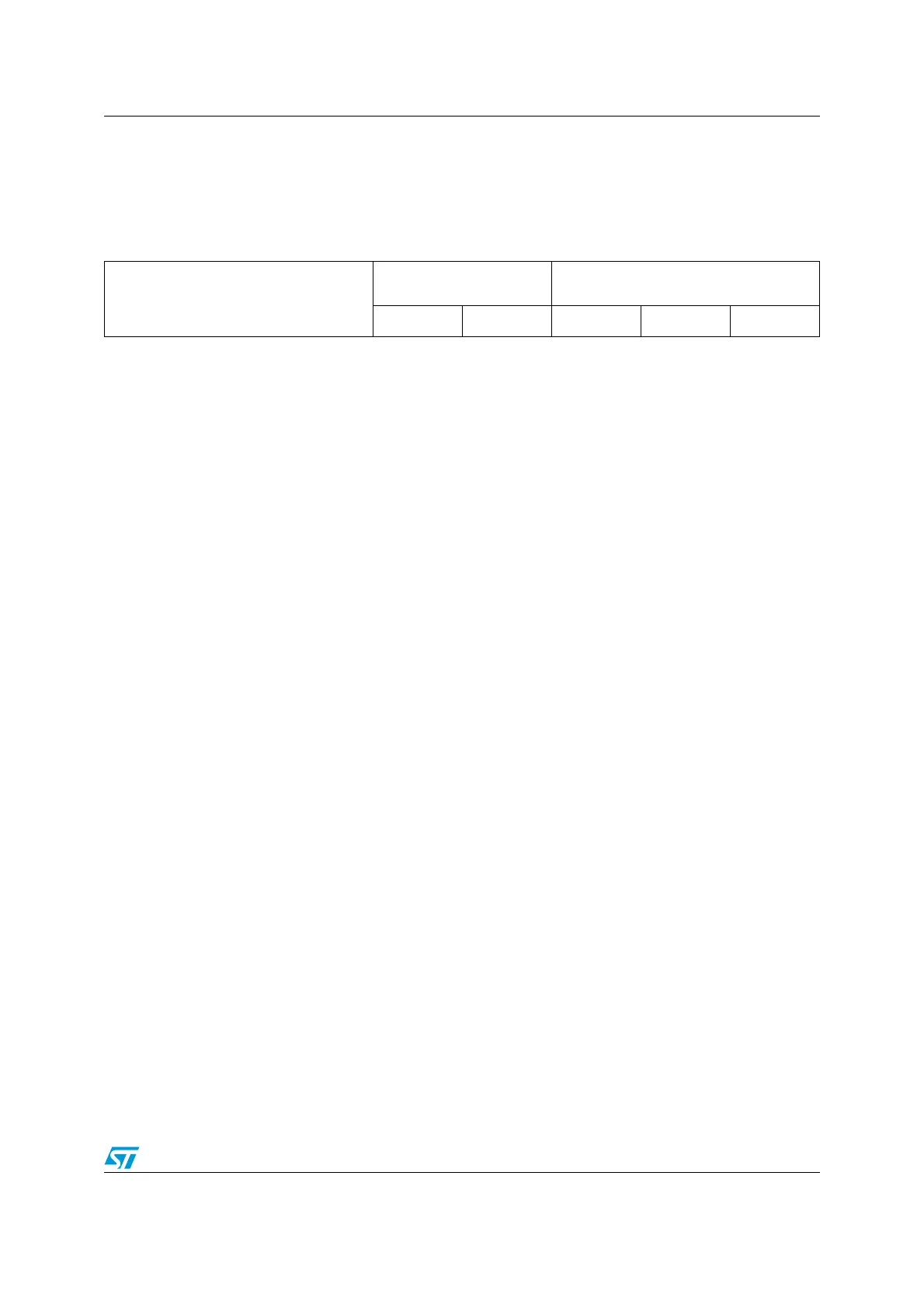

9.9.6 Clock divider register (CLK_CKDIVR)

Address offset: 0x06

Reset value: 0x18

76543210

Reserved

HSIDIV[1:0] CPUDIV[2:0]

rw rw rw rw rw

Bits 7:5 Reserved, must be kept cleared.

Bits 4:3 HSIDIV[1:0]: High speed internal clock prescaler

These bits are written by software to define the HSI prescaling factor.

00: f

HSI

= f

HSI RC output

01: f

HSI

= f

HSI RC output

/2

10: f

HSI

= f

HSI RC output

/4

11: f

HSI

= f

HSI RC output

/8

Bits 2:0 CPUDIV[2:0]: CPU clock prescaler

These bits are written by software to define the CPU clock prescaling factor.

000: f

CPU

=f

MASTER

001: f

CPU

=f

MASTER

/2

010: f

CPU

=f

MASTER

/4

011: f

CPU

=f

MASTER

/8

100: f

CPU

=f

MASTER

/16

101: f

CPU

=f

MASTER

/32

110: f

CPU

=f

MASTER

/64

111: f

CPU

=f

MASTER

/128

Loading...

Loading...