16-bit advanced control timer (TIM1) RM0016

142/449 Doc ID 14587 Rev 8

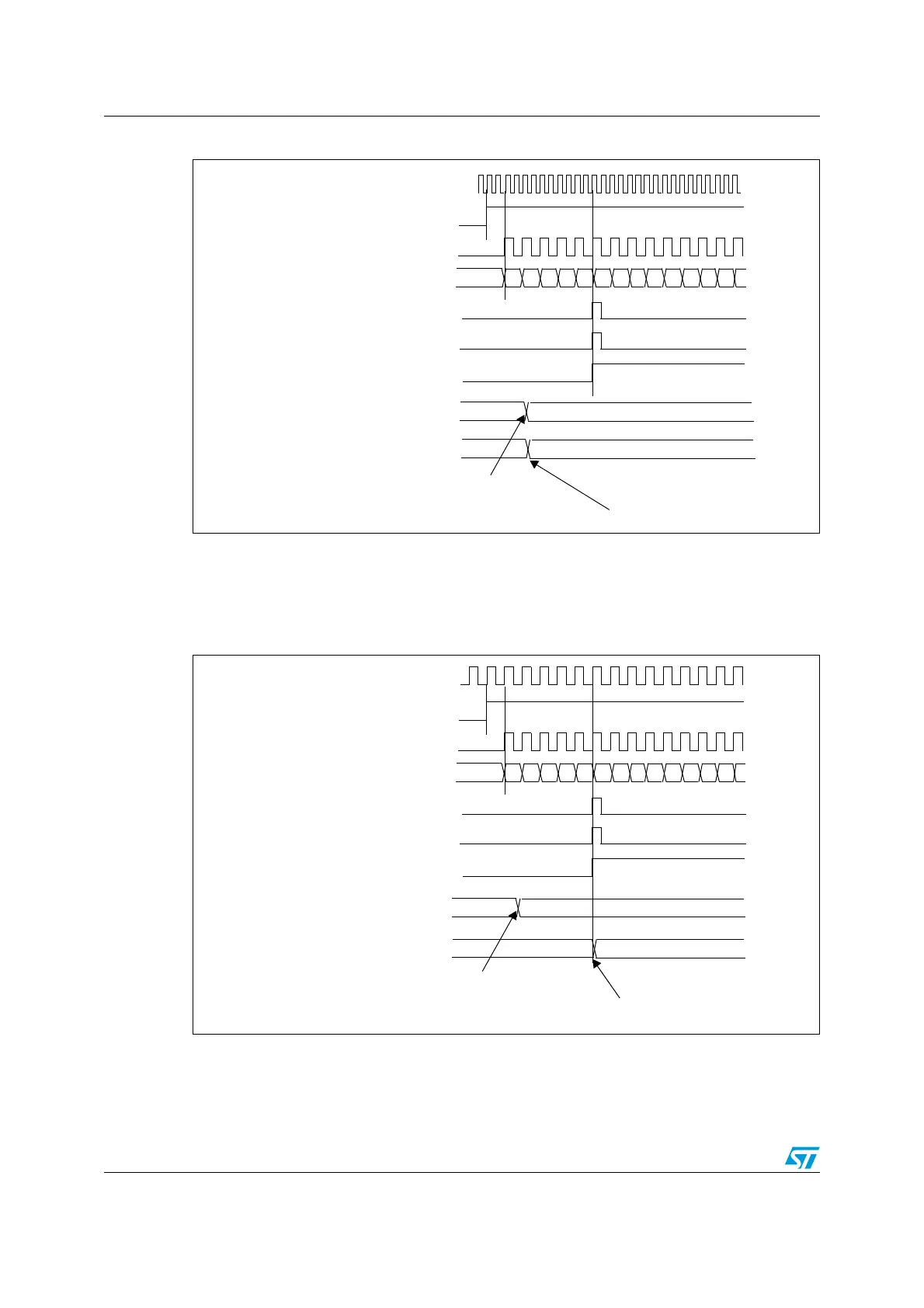

Figure 35. Counter update when ARPE = 0 (ARR not preloaded) with prescaler = 2

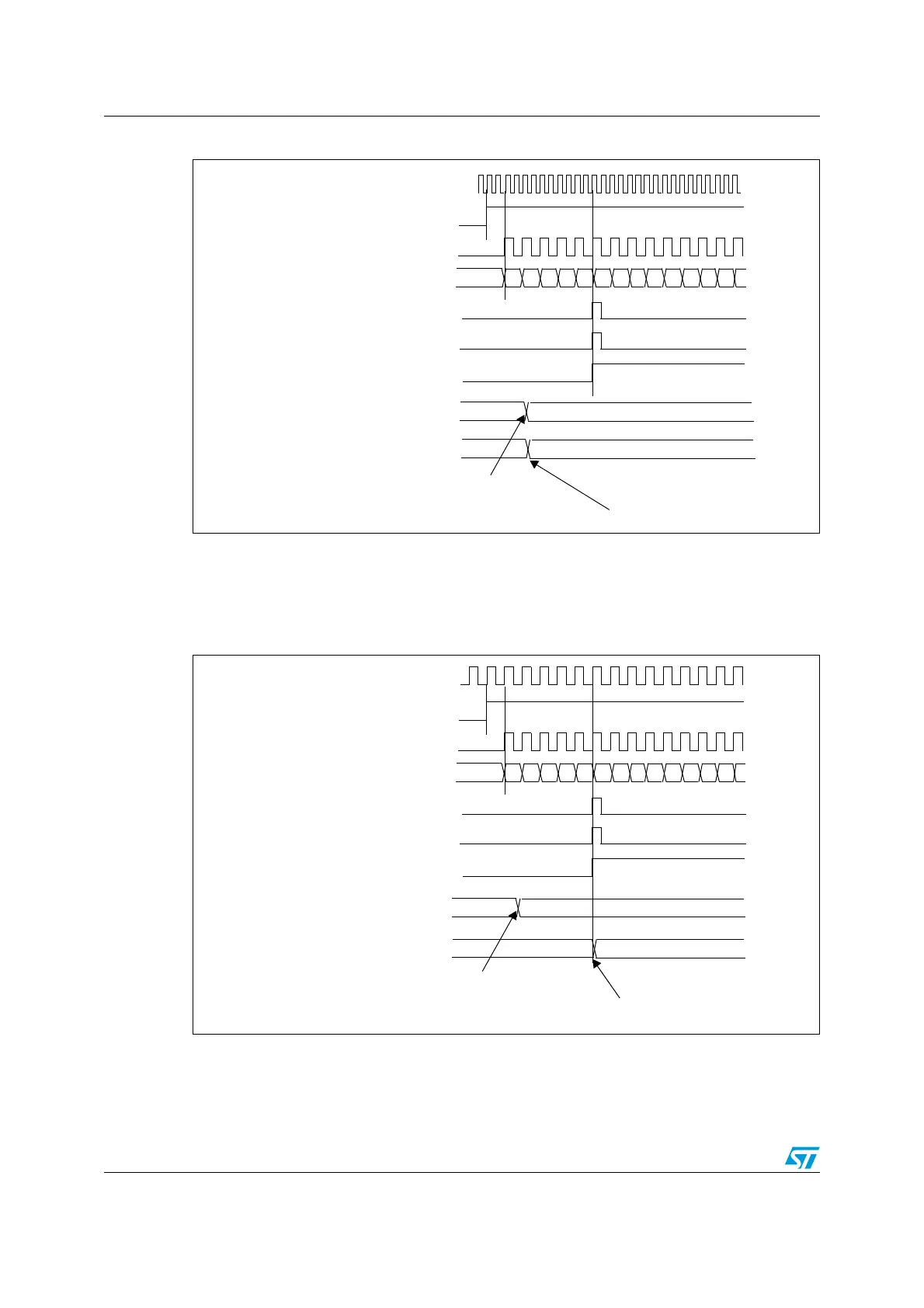

In Figure 36 the prescaler divider is set to 1, so CK_CNT has the same frequency as

CK_PSC. The auto-reload preload is enabled (ARPE = 1), so the next counter overflow

occurs at 0xFF. The new auto-reload value register value of 36h is taken into account after

the overflow which generates a UEV.

Figure 36. Counter update event when ARPE = 1 (TIM1_ARR preloaded)

CK_PSC

00

CNT_EN

TIMER CLOCK = CK_CNT

COUNTER REGISTER

UPDATE INTERRUPT FLAG (UIF)

COUNTER OVERFLOW

UPDATE EVENT (UEV)

01 02 03 04 05 06 0732 33 34 35 3631

AUTO-RELOAD PRELOAD REGISTER

FF 36

AUTO-RELOAD SHADOW REGISTER

Write a new value in TIMx_ARR

FF 36

New value transferred immediately in shadow register

00

CNT_EN

TIMER CLOCK = CK_CNT

COUNTER REGISTER

UPDATE INTERRUPT FLAG (UIF)

COUNTER OVERFLOW

UPDATE EVENT (UEV)

01 02 03 04 05 06 07FB FC FD FE FFFA

AUTO-RELOAD PRELOAD REGISTER

FF 36

AUTO-RELOAD SHADOW REGISTER

FF 36

Write a new value in TIMx_ARR

CK_PSC

New value transferred in shadow register

on counter overflow

Loading...

Loading...