Central processing unit (CPU) RM0016

28/449 Doc ID 14587 Rev 8

1.3.2 SWIM disable

By default, after an MCU reset, the SWIM pin is configured to allow communication with an

external tool for debugging or Flash/EEPROM programming. This pin can be configured by

the application for use as a general purpose I/O. This is done by setting the SWD bit in the

CFG_GCR register.

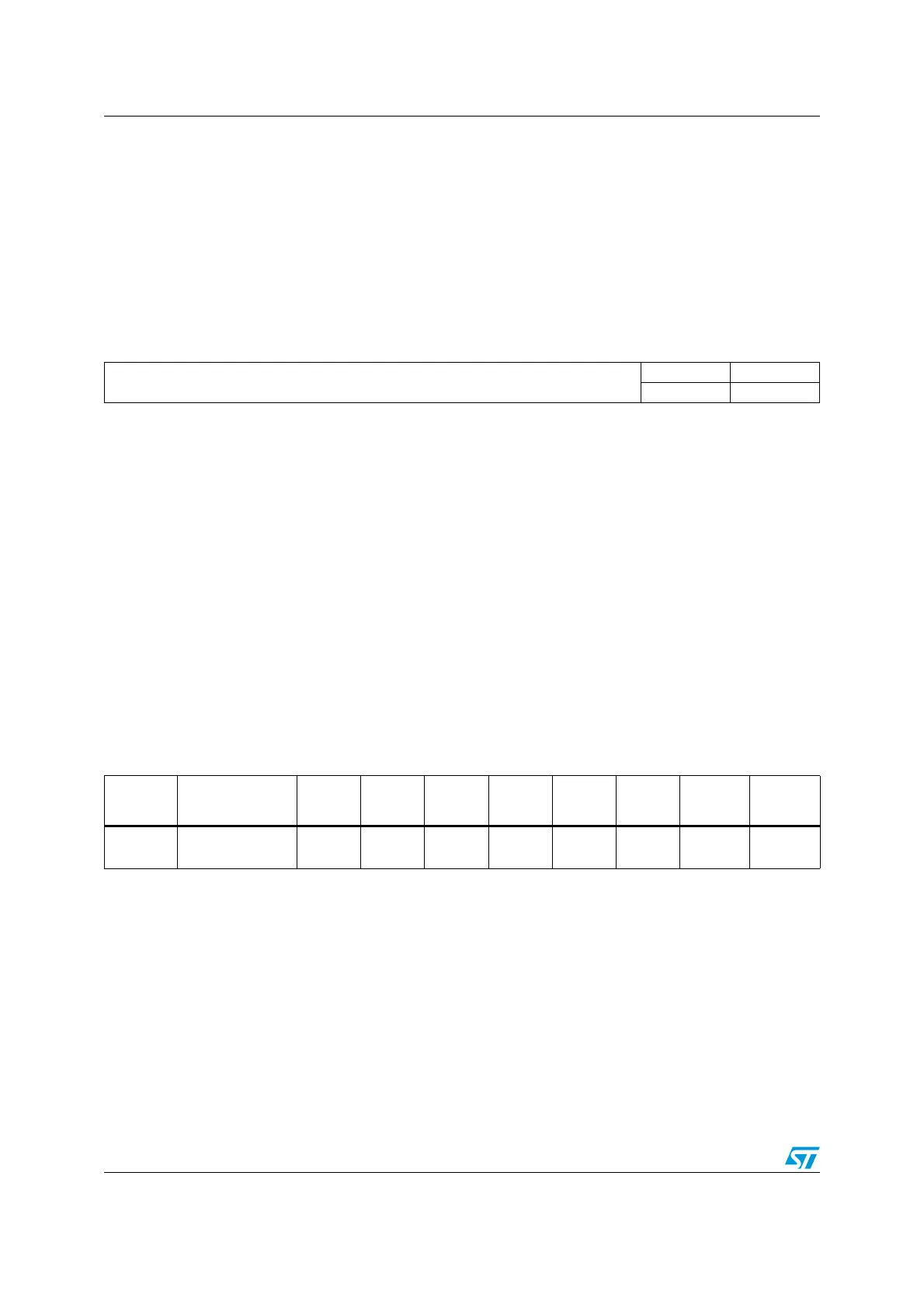

1.3.3 Description of global configuration register (CFG_GCR)

Address offset: 0x00

Reset value: 0x00

1.3.4 Global configuration register map and reset values

The CFG_GCR is mapped in the STM8 address space. Refer to the corresponding

datasheets for the base address.

76543210

Reserved

AL SWD

rw rw

Bits 7:2 Reserved

Bit 1 AL: Activation level

This bit is set and cleared by software. It configures main or interrupt-only activation.

0: Main activation level. An IRET instruction causes the context to be retrieved from the stack and

the main program continues after the WFI instruction.

1: Interrupt-only activation level. An IRET instruction causes the CPU to go back to WFI/Halt mode

without restoring the context.

Bit 0 SWD: SWIM disable

0: SWIM mode enabled

1: SWIM mode disabled

When SWIM mode is enabled, the SWIM pin cannot be used as general purpose I/O.

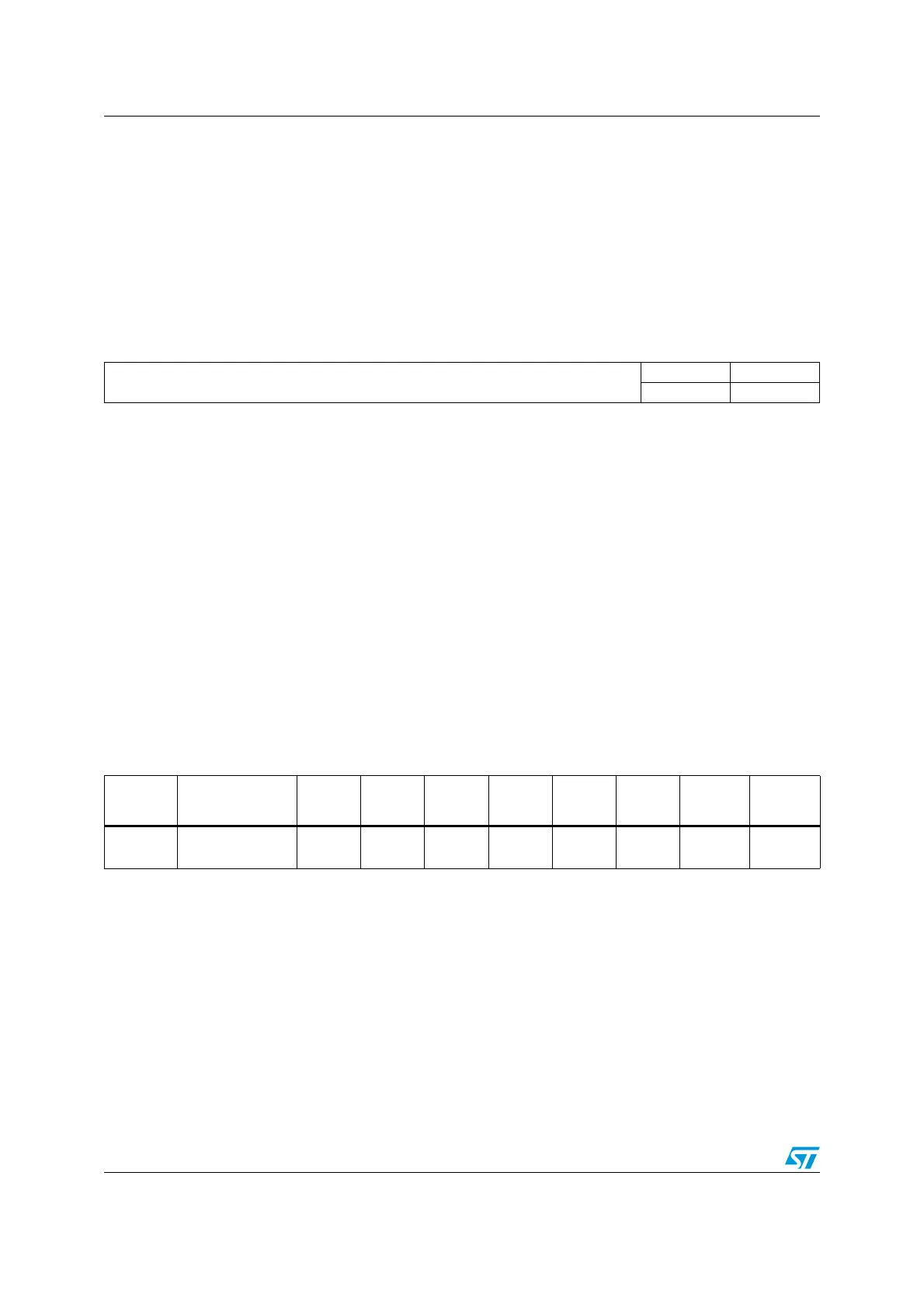

Table 3. CFG_GCR register map

Address

offset

Register name765432 1 0

0x00

CFG_GCR

Reset value

-

0

-

0

-

0

-

0

-

0

-

0

AL

0

SWD

0

Loading...

Loading...