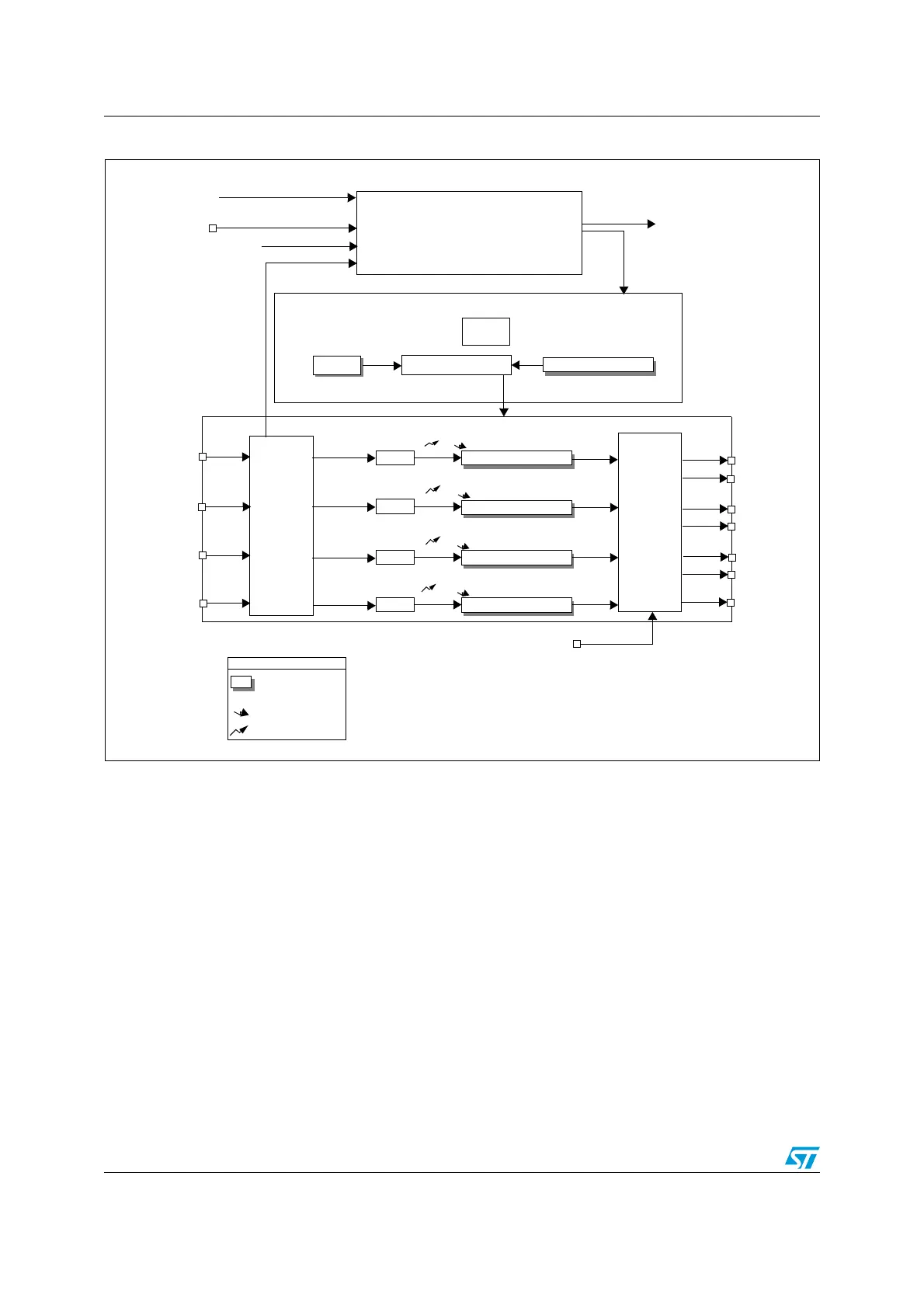

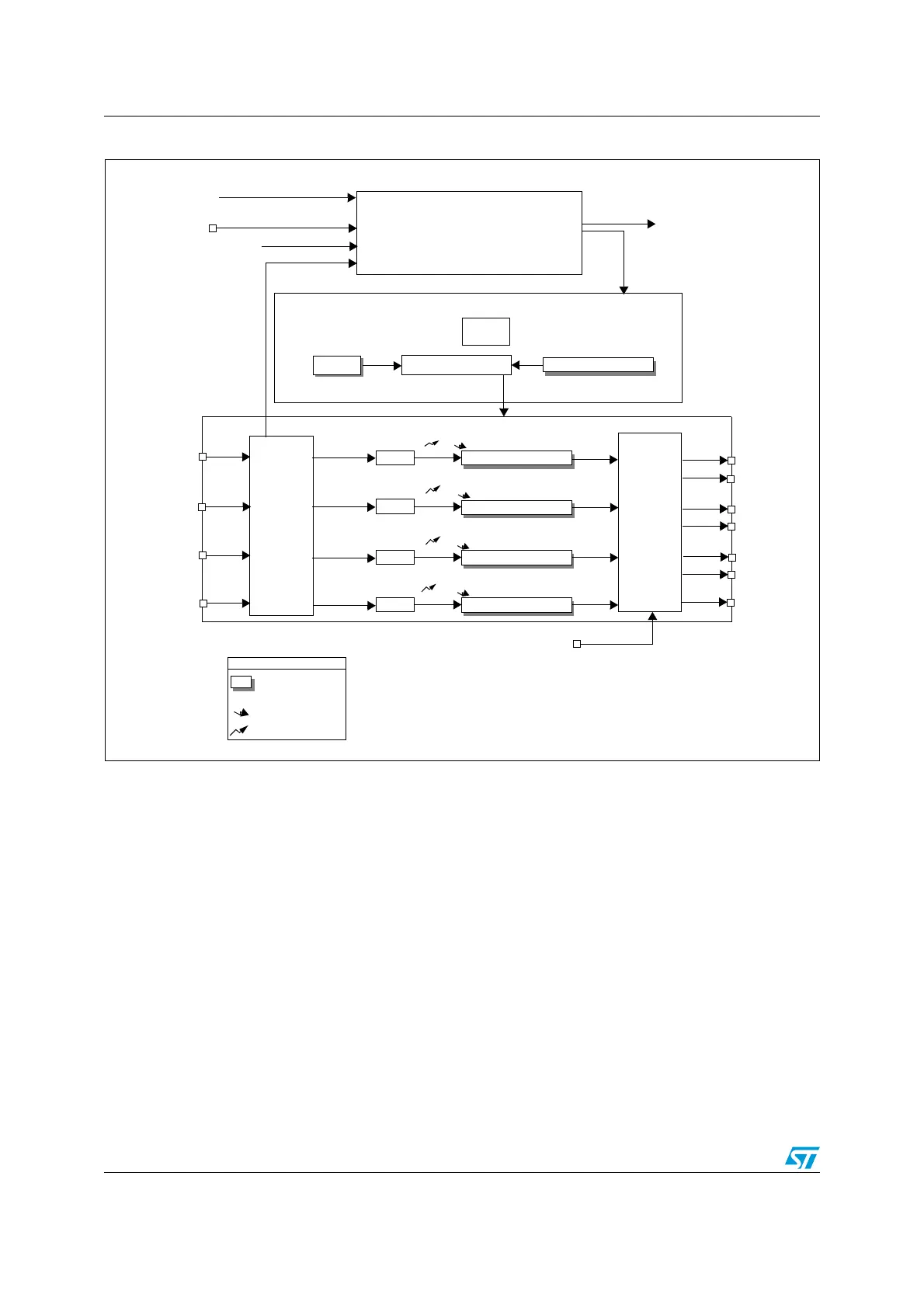

Figure 31. TIM1 general block diagram

Repetition

counter

Prescaler

Auto-reload register

UP-DOWN COUNTER

Capture/Compare 1 Register

Capture/Compare 2 Register

UEV

ETR

f

MASTER/DIV

Capture/Compare 3 Register

OC1REF

OC2REF

OC3REF

CK_PSC

Prescaler

IC3PS

IC1

IC2

Prescaler

Prescaler

IC2PS

IC1PS

IC3

CC1I

CC2I

CC3I

TIM1_CH2

TIM1_CH3

OC1

OC2

OC3

TIM1_BKIN

TIM1_ETR

TIM1_CH3N

OC3N

OC2N

OC1N

CK_CNT

Capture/Compare 4 Register

OC4REF

Prescaler

IC4PS

IC4

TIM1_CH4

CC4I

UEV

UEV

UEV

TIME BASE UNIT

CLOCK/TRIGGER CONTROLLER

INPUT

OUTPUT

CAPTURE COMPARE ARRAY

TIM1_CH2N

TIM1_CH1N

TI1

TI2

TI3

TI4

OC4

TIM1_CH2

TIM1_CH1

STAGE

STAGE

TIM1_CH1

TIM1_CH3

TIM1_CH4

ITR

TRGO from other TIM timers

TRGO to TIM5/TIM6 or to ADC

event

Legend:

Preload registers transferred

to shadow registers on update

interrupt

event (UEV) according to

control bit

TRC

Clock/reset/enable

Reg

Loading...

Loading...