Universal asynchronous receiver transmitter (UART) RM0016

310/449 Doc ID 14587 Rev 8

The following pin is required to interface in synchronous mode:

UART_CK: Transmitter clock output. This pin outputs the transmitter data clock for

synchronous transmission (no clock pulses on start bit and stop bit, and a software

option to send a clock pulse on the last data bit). This can be used to control

peripherals that have shift registers (e.g. LCD drivers). The clock phase and polarity

are software programmable.

The UART_RX and UART_TX pins are used in IrDA mode as follows:

UART_RX = IrDA_RDI: Receive Data Input in IrDA mode

UART_TX = IrDA_TDO: Transmit Data Output in IrDA mode

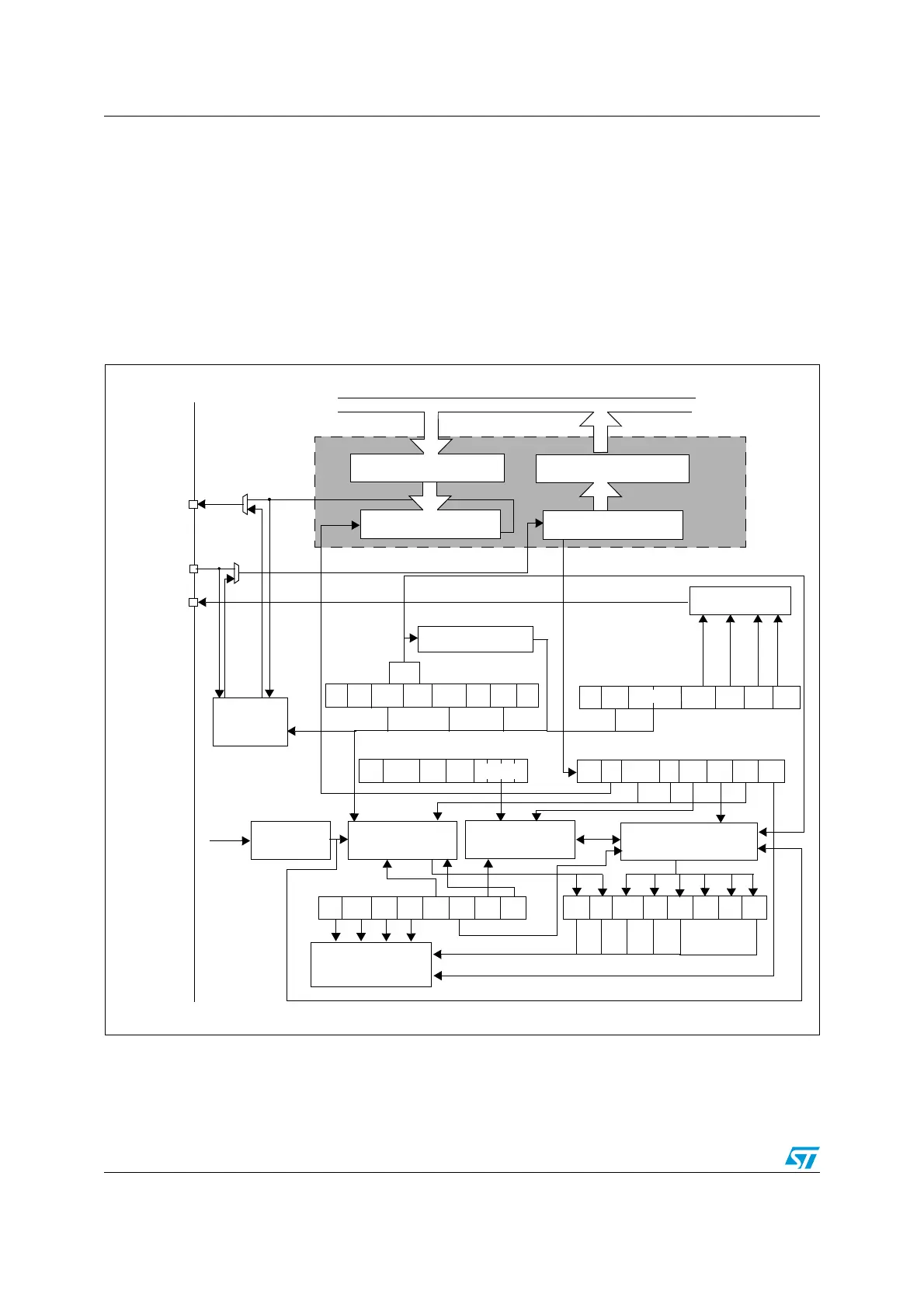

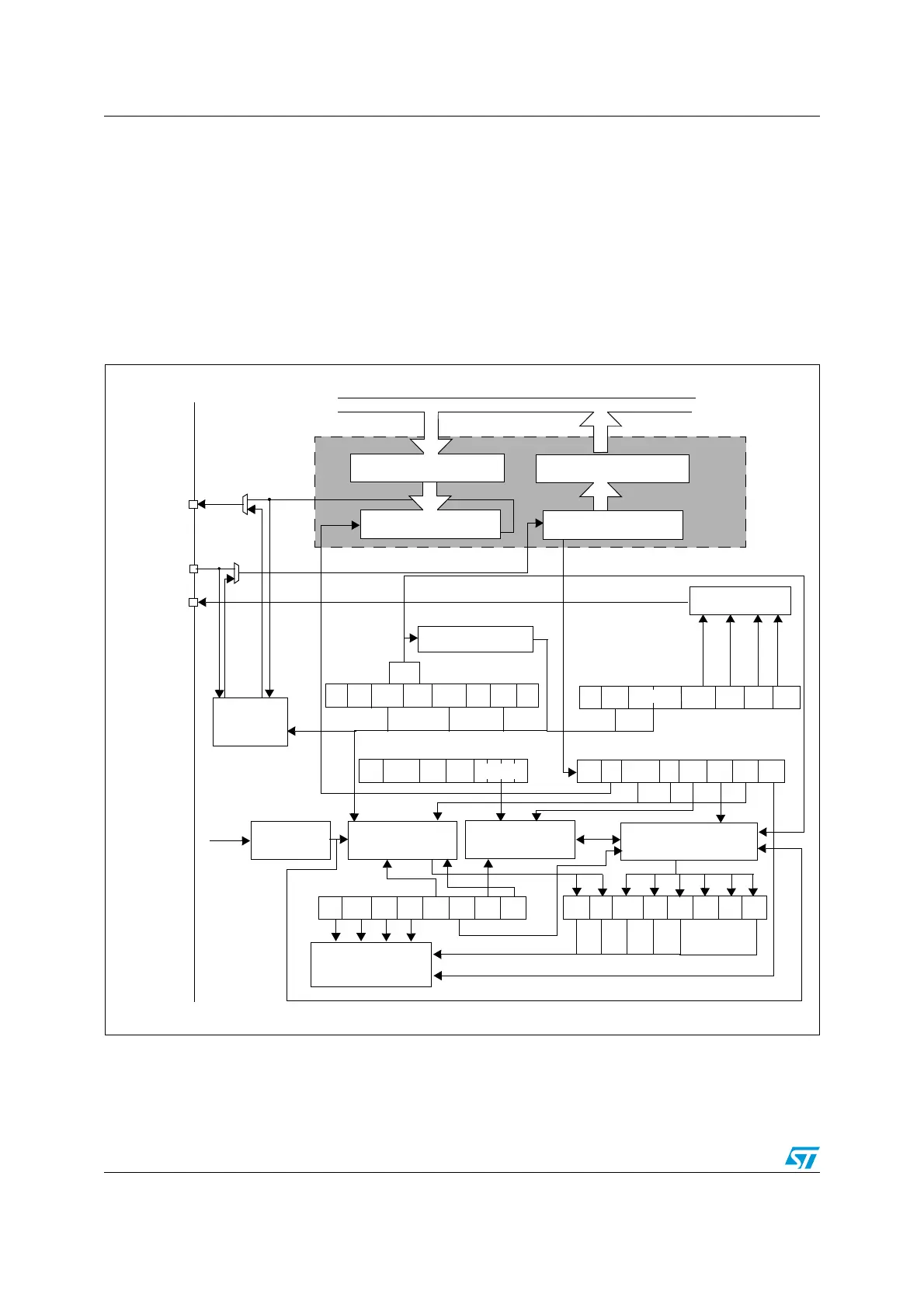

Figure 110. UART1 block diagram

WAKE_UP

UNIT

RECEIVER

CONTROL

UART1_SR

TRANSMIT

CONTROL

TXE TC RXNE IDLE OR NF FE

CONTROL

INTERRUPT

UART1_CR1

R8 T8 M WAKE

Receive Data Register (RDR)

Receive Shift Register

Read

Transmit Data Register (TDR)

Transmit Shift Register

Write

UART1_TX

UART1_DR

(DATA REGISTER)

BAUD RATE

f

MASTER

GENERATOR

SBKRWURENTENILIENRIENTCIENTIEN

UART1_CR2

UARTD PCEN PS

PIEN

PE

IRLPSCEN IREN--

UART1_CR4

UART1_CR5

IrDA

SIR ENDEC

BLOCK

LINEN

-

CLKEN CPOL CPHA LBCL

UART_CK CONTROL

UART1_CK

UART1_CR3

GUARD TIME REGISTER

STOP BITS

-NACK

UART1_BRR

HDSEL

LBDIEN ADDLBDL LBDF

UART1_RX

MCU bus

-

UART1_GTR

Loading...

Loading...