Interrupt controller (ITC) RM0016

66/449 Doc ID 14587 Rev 8

6.8 Interrupt mapping

Refer to the corresponding device datasheet for the table of interrupt vector addresses.

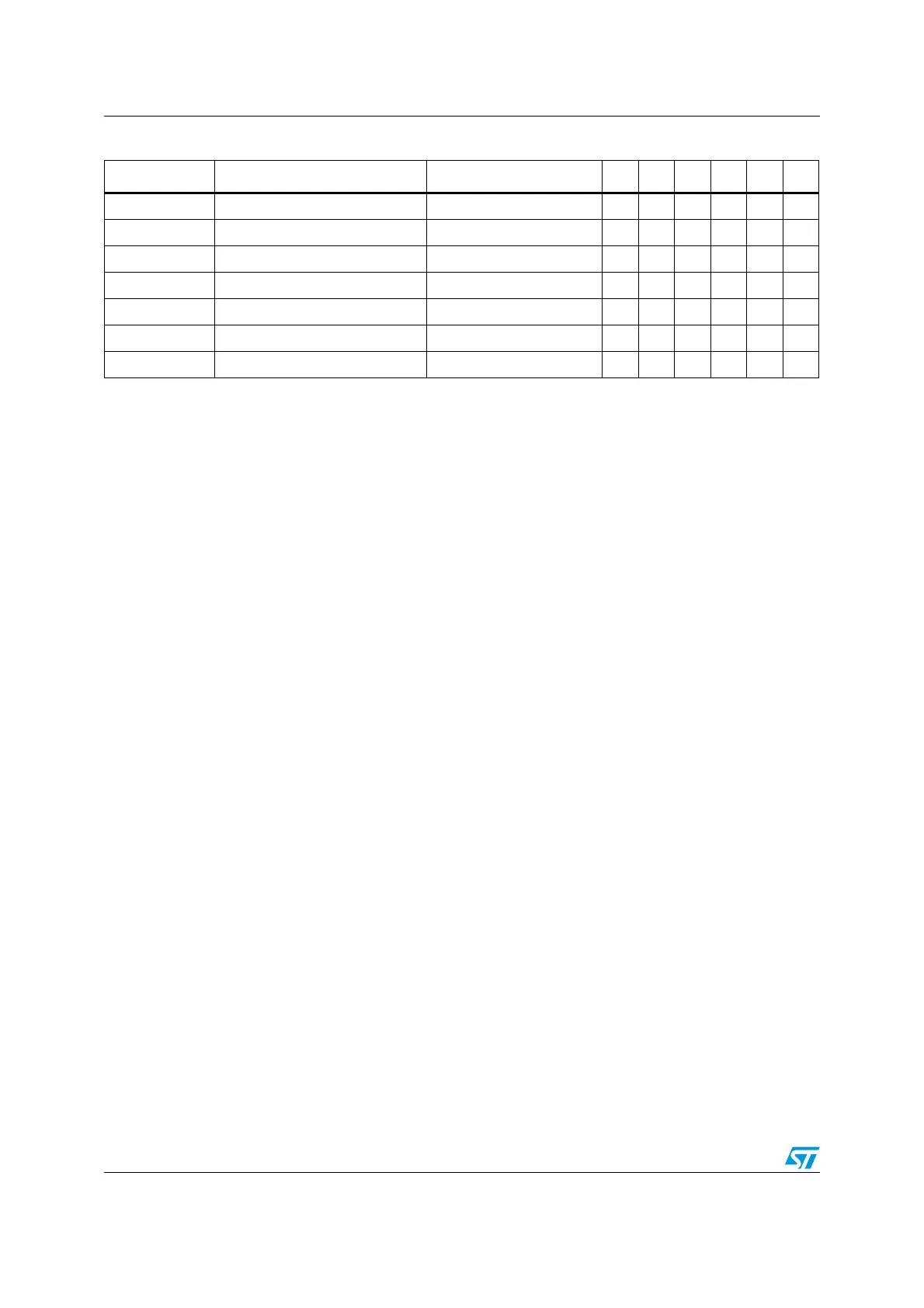

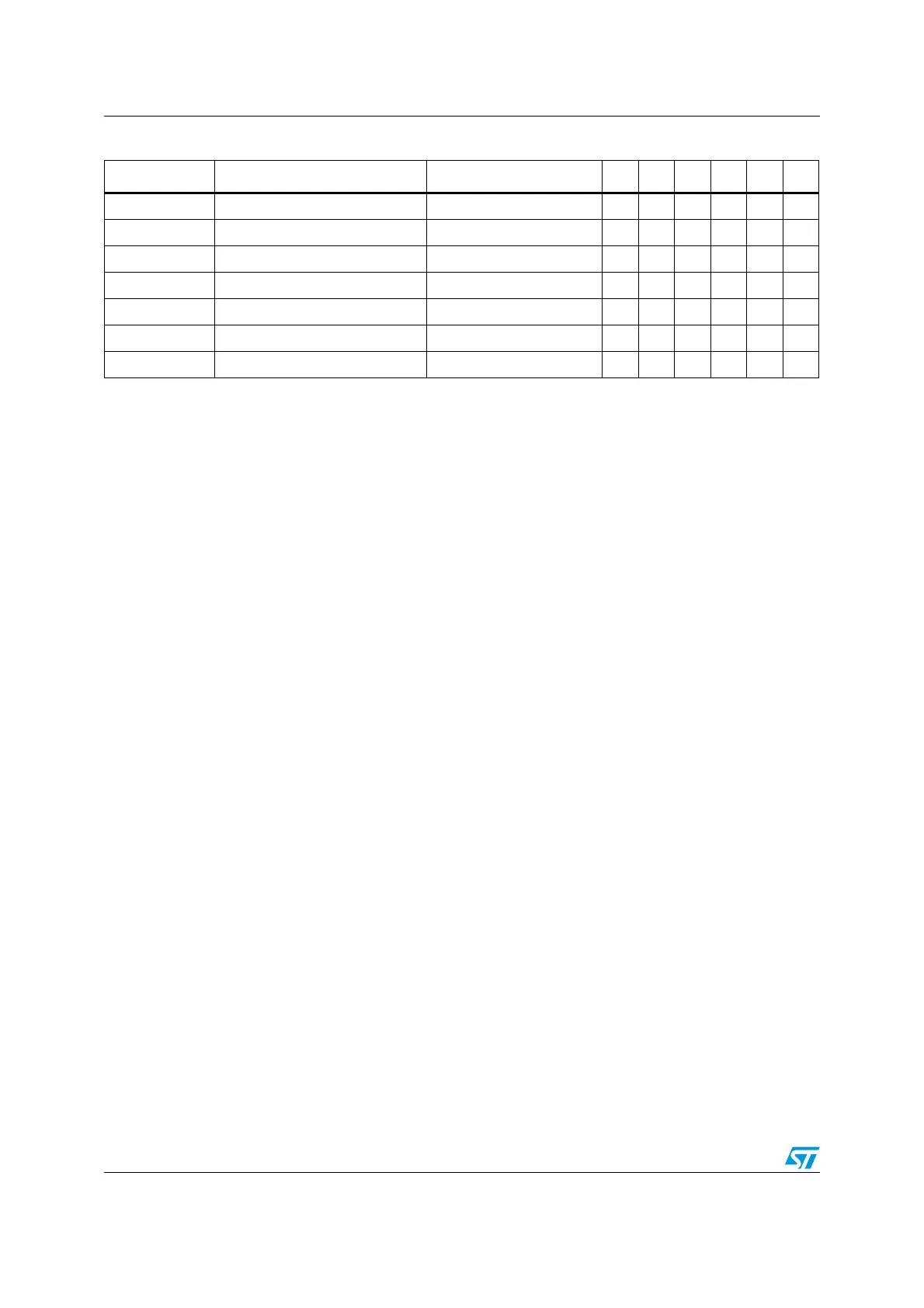

JRNM Jump if I1:0<>11 I1:0<>11 ?

POP CC Pop CCR from the stack Memory => CCR I1 H I0 N Z C

PUSH CC Push CC on the stack CC =>Memory

RIM Enable interrupt (level 0 set) Load 10 in I1:0 of CCR 1 0

SIM Disable interrupt (level 3 set) Load 11 in I1:0 of CCR 1 1

TRAP Software trap Software NMI 1 1

WFI Wait for interrupt 1 0

Table 11. Dedicated interrupt instruction set (continued)

Instruction New description Function/example I1 H I0 N Z C

Loading...

Loading...