Clock control (CLK) RM0016

92/449 Doc ID 14587 Rev 8

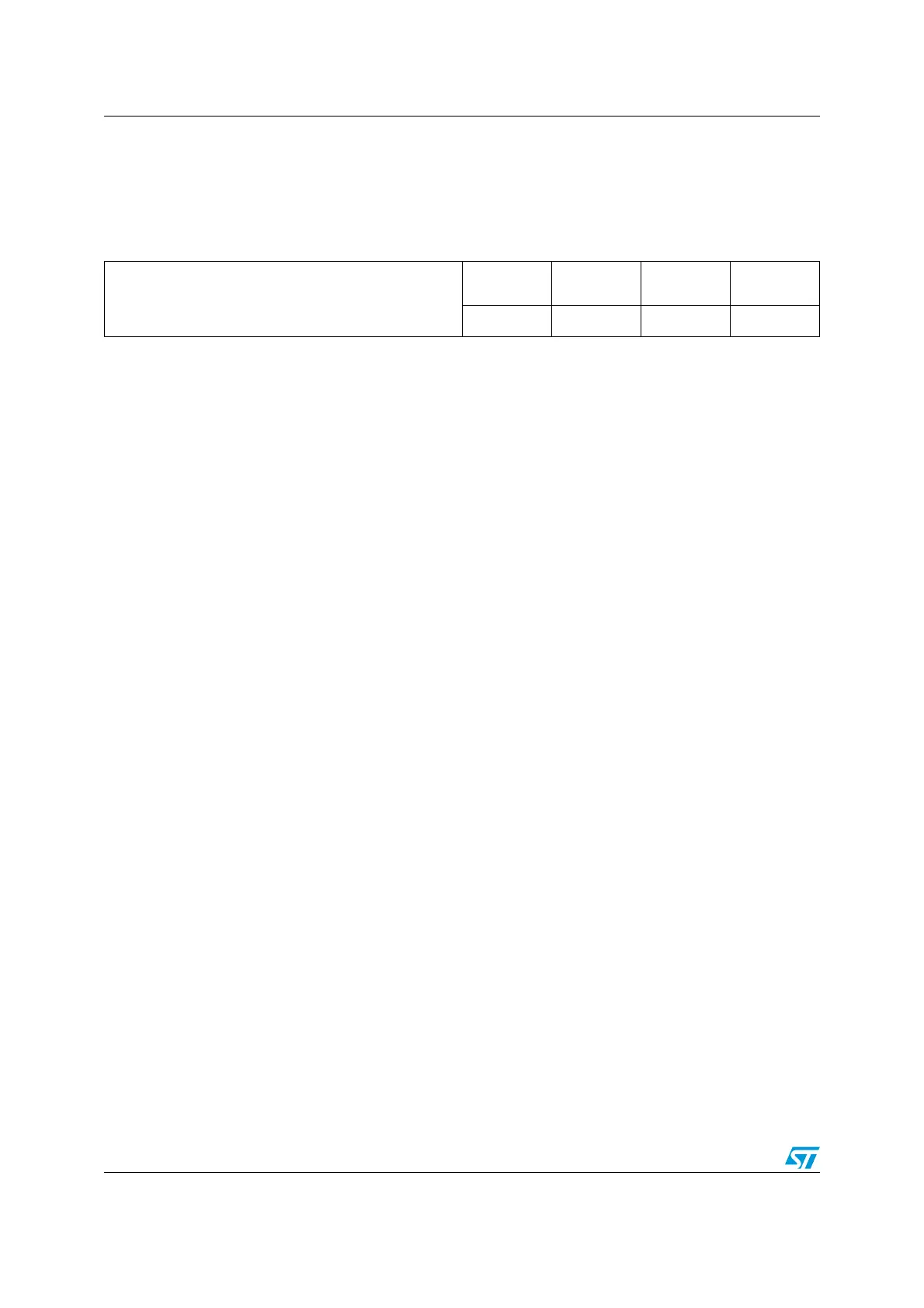

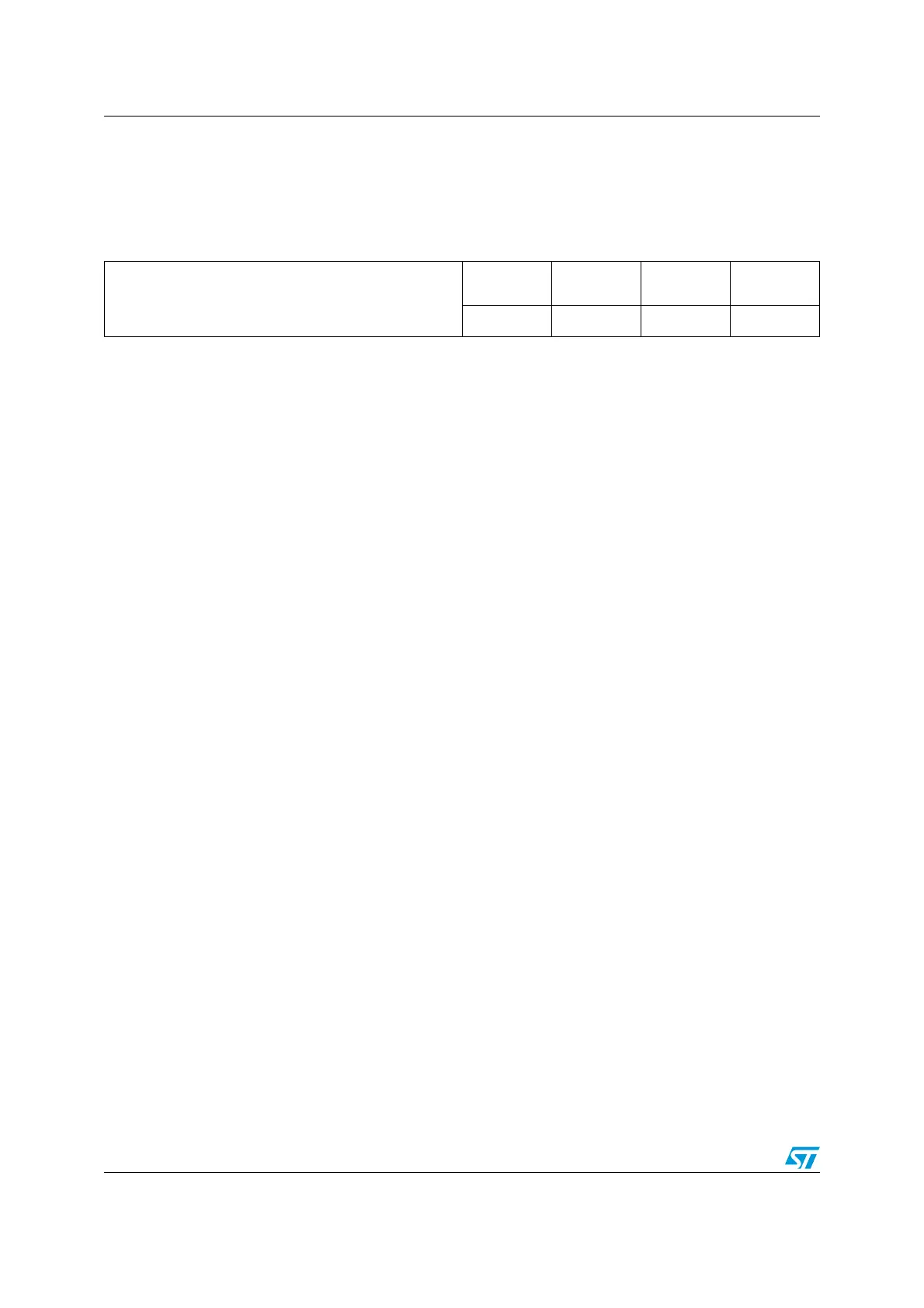

9.9.5 Switch control register (CLK_SWCR)

Address offset: 0x05

Reset value: 0xXX

76543210

Reserved

SWIF SWIEN SWEN SWBSY

rc_w0 rw rw rw

Bits 7:4 Reserved.

Bit 3 SWIF: Clock switch interrupt flag

This bit is set by hardware and cleared by software writing 0. Its meaning depends on the status of

the SWEN bit. Refer to Figure 22 and Figure 23.

● In manual switching mode (SWEN = 0):

0: Target clock source not ready

1: Target clock source ready

● In automatic switching mode (SWEN = 1):

0: No clock switch event occurred

1: Clock switch event occurred

Bit 2 SWIEN: Clock switch interrupt enable

This bit is set and cleared by software.

0: Clock switch interrupt disabled

1: Clock switch interrupt enabled

Bit 1 SWEN: Switch start/stop

This bit is set and cleared by software. Writing a 1 to this bit enables switching the master clock to

the source defined in the CLK_SWR register.

0: Disable clock switch execution

1: Enable clock switch execution

Bit 0 SWBSY: Switch busy

This bit is set and cleared by hardware. It can be cleared by software to reset the clock switch

process.

0: No clock switch ongoing

1: Clock switch ongoing

Loading...

Loading...