RM0016 Independent watchdog (IWDG)

Doc ID 14587 Rev 8 125/449

14.3.3 Reload register (IWDG_RLR)

Address offset: 0x02

Reset value: 0xFF

14.3.4 IWDG register map and reset values

76543210

RL[7:0]

rw

Bits 7:0

RL[7:0]: Watchdog counter reload value

These bits are write access protected (see Section 14.2). They are written by software to define the

value to be loaded in the watchdog counter each time the value 0xAA is written in the IWDG_KR

register. The watchdog counter counts down from this value. The timeout period is a function of this

value and the clock prescaler. Refer to Ta bl e 2 8.

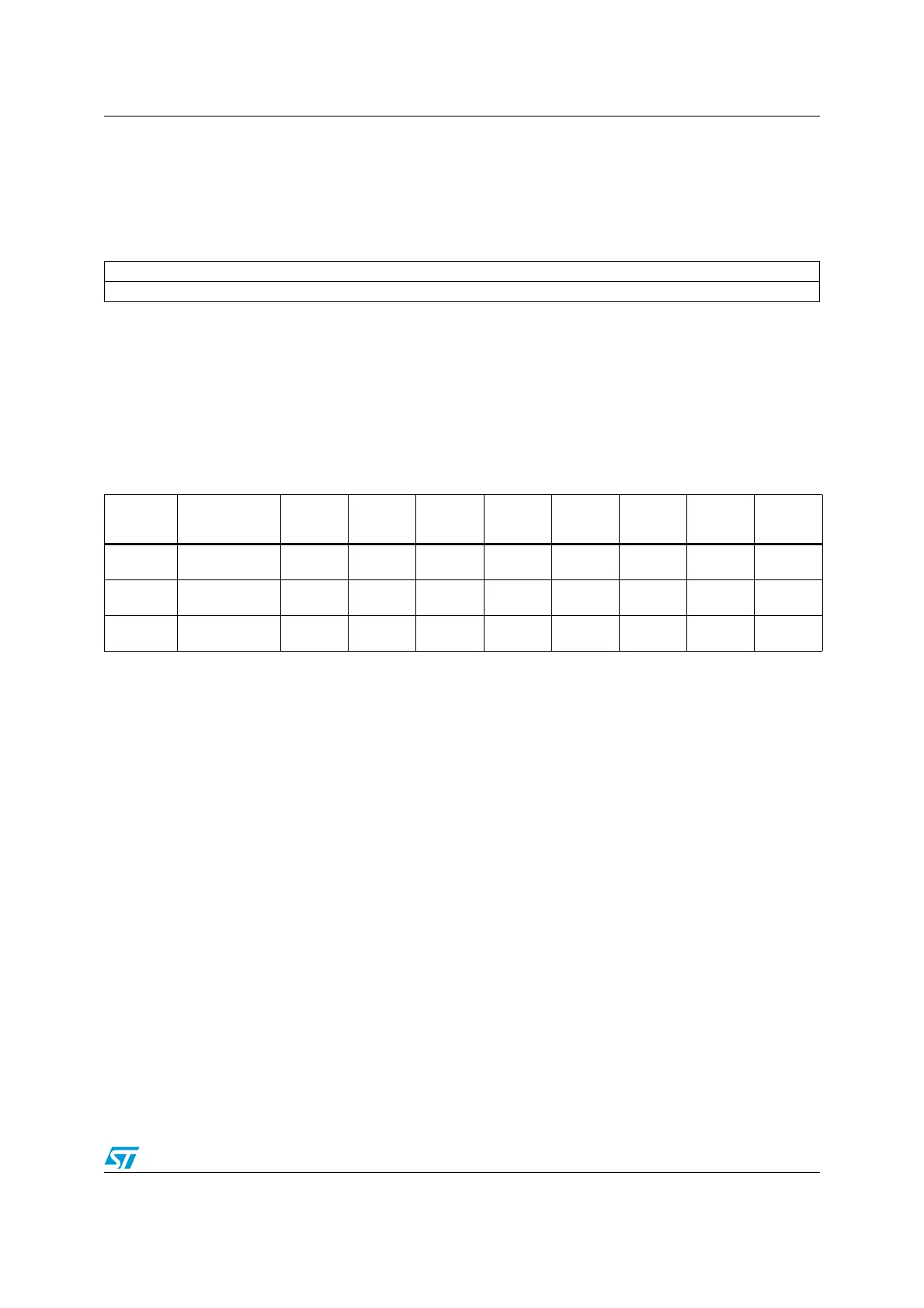

Table 29. IWDG register map

Address

offset

Register

name

76543210

0x00

IWDG_KR

Reset value

KEY7

x

KEY6

x

KEY5

x

KEY4

x

KEY3

x

KEY2

x

KEY1

x

KEY0

x

0x01

IWDG_PR

Reset value

-

0

-

0

-

0

-

0

-

0

PR2

0

PR1

0

PR0

0

0x02

IWDG_RLR

Reset value

RL7

1

RL6

1

RL5

1

RL4

1

RL3

1

RL2

1

RL1

1

RL0

1

Loading...

Loading...