16-bit general purpose timers (TIM2, TIM3, TIM5) RM0016

224/449 Doc ID 14587 Rev 8

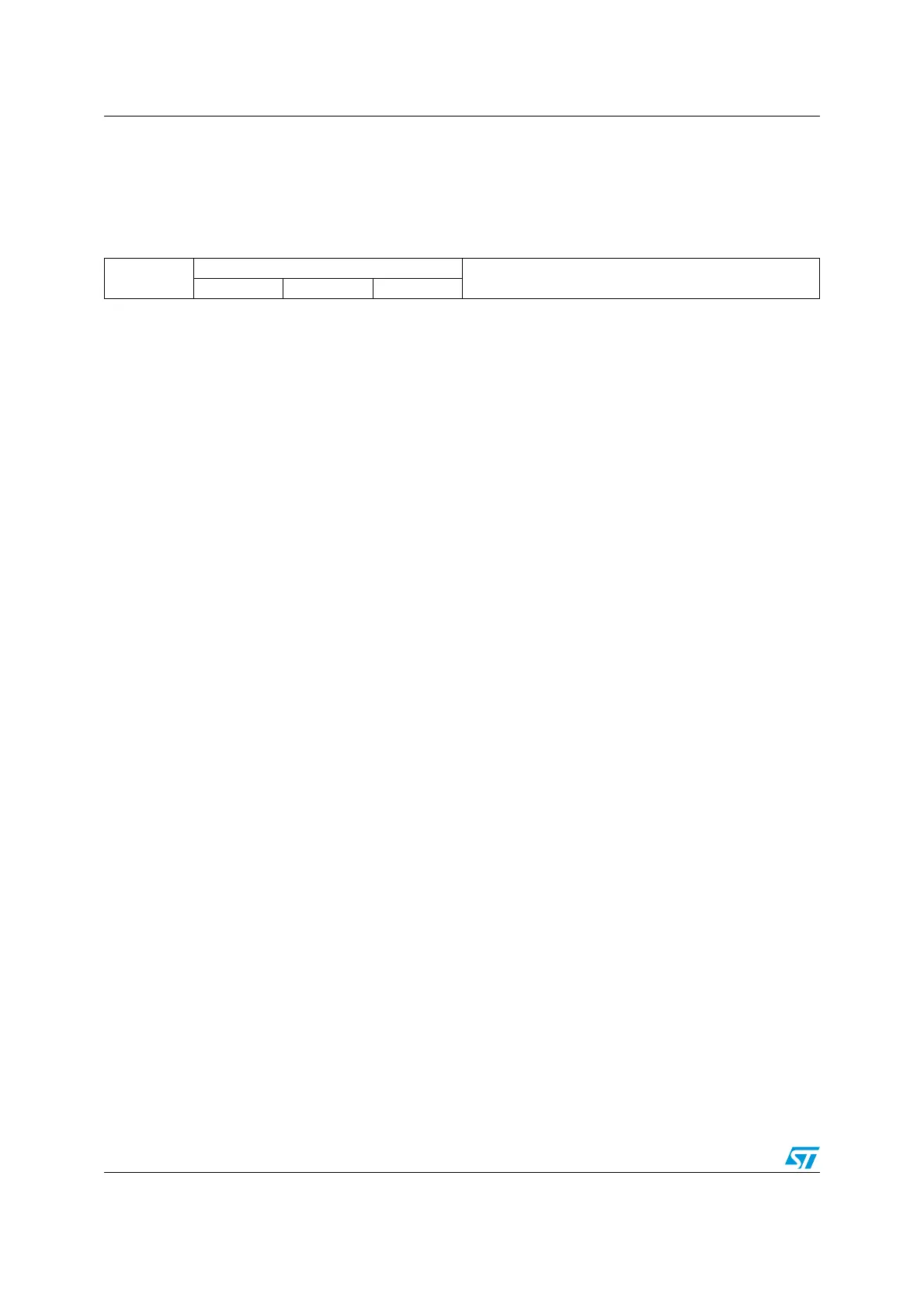

18.6.2 Control register 2 (TIM5_CR2)

Address offset: 0x01

Reset value: 0x00

Note: This register is only available in TIM5, see Table 42 on page 241.

76543210

Reserved

MMS[2:0]

Reserved

rw rw rw

Bit 7 Reserved, must be kept cleared

Bits 6:4 MMS[2:0]: Master mode selection

These bits select the information to be sent in master mode to TIM1 and TIM2for synchronization

(TRGO). The combination is as follows:

000: Reset - the UG bit from the TIM5_EGR register is used as a trigger output (TRGO). If the reset

is generated by the trigger input (clock/trigger mode controller configured in trigger reset mode), the

signal on TRGO is delayed compared to the actual reset.

001: Enable - the counter enable signal is used as a trigger output (TRGO). It is used to start several

timers at the same time or to control a window in which a slave timer is enabled. The counter enable

signal is generated by a logic OR between the CEN control bit and the trigger input when configured

in gated mode. When the counter enable signal is controlled by the trigger input, there is a delay on

TRGO, except if the master/slave mode is selected (see the MSM bit description in TIM5_SMCR

register).

010: Update - The update event is selected as a trigger output (TRGO)

011: Reserved

100: Reserved

101: Reserved

111: Reserved

Bits 3:0 Reserved, must be kept cleared

Loading...

Loading...