Inter-integrated circuit (I

2

C) interface RM0016

302/449 Doc ID 14587 Rev 8

Note: Reading I2C_SR3 after reading I2C_SR1 clears the ADDR flag, even if the ADDR flag was

set after reading I2C_SR1. Consequently, I2C_SR3 must be read only when ADDR is found

set in I2C_SR1 or when the STOPF bit is cleared.

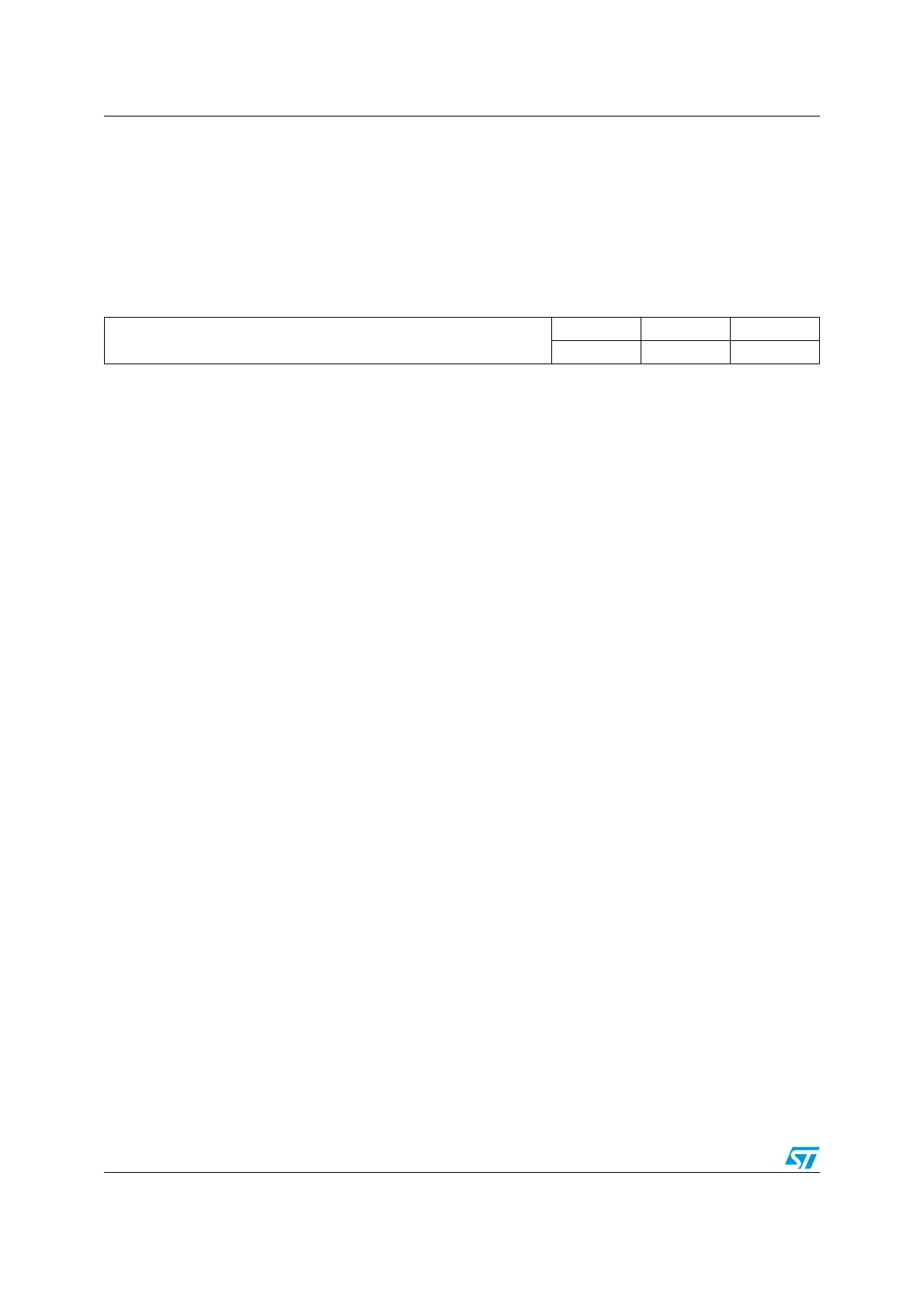

21.7.10 Interrupt register (I2C_ITR)

Address offset: 0x0A

Reset value: 0x00

76543210

Reserved

ITBUFEN ITEVTEN ITERREN

rw rw rw

Bits 7:3 Reserved

Bit 2 ITBUFEN: Buffer interrupt enable

0: TXE = 1 or RXNE = 1 does not generate any interrupt.

1:TXE = 1 or RXNE = 1 generates Event interrupt.

Bit 1 ITEVTEN: Event interrupt enable

0: Event interrupt disabled

1: Event interrupt enabled

This interrupt is generated when:

– SB = 1 (Master)

– ADDR = 1 (Master/Slave)

– ADD10= 1 (Master)

–STOPF = 1 (Slave)

– BTF = 1 with no TXE or RXNE event

– TXE event to 1 if ITBUFEN = 1

– RXNE event to 1if ITBUFEN = 1

– WUFH = 1 (asynchronous interrupt to wakeup from Halt)

Bit 0 ITERREN: Error interrupt enable

0: Error interrupt disabled

1: Error interrupt enabled

– This interrupt is generated when:

–BERR = 1

–ARLO = 1

–AF = 1

–OVR = 1

Loading...

Loading...