Universal asynchronous receiver transmitter (UART) RM0016

356/449 Doc ID 14587 Rev 8

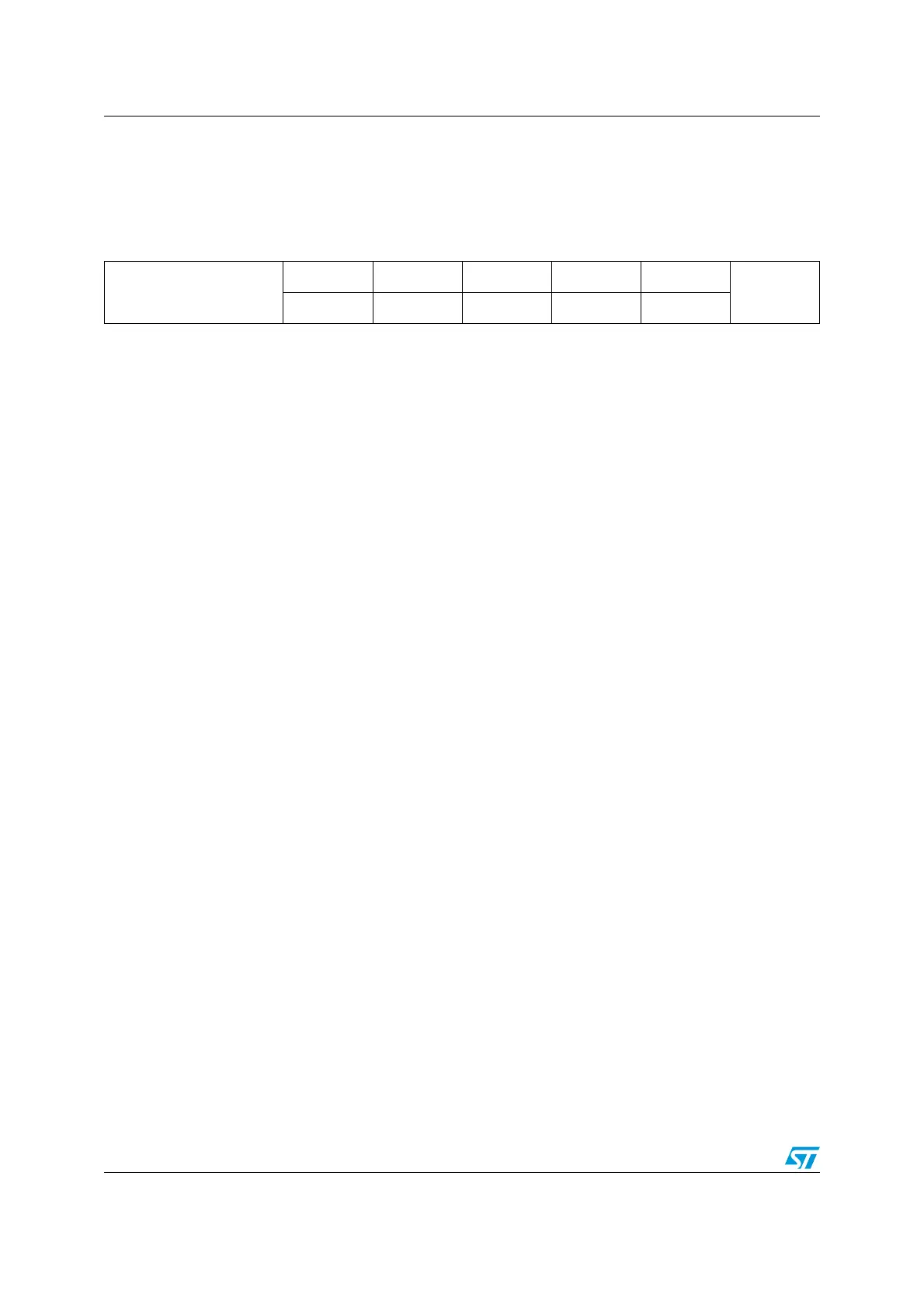

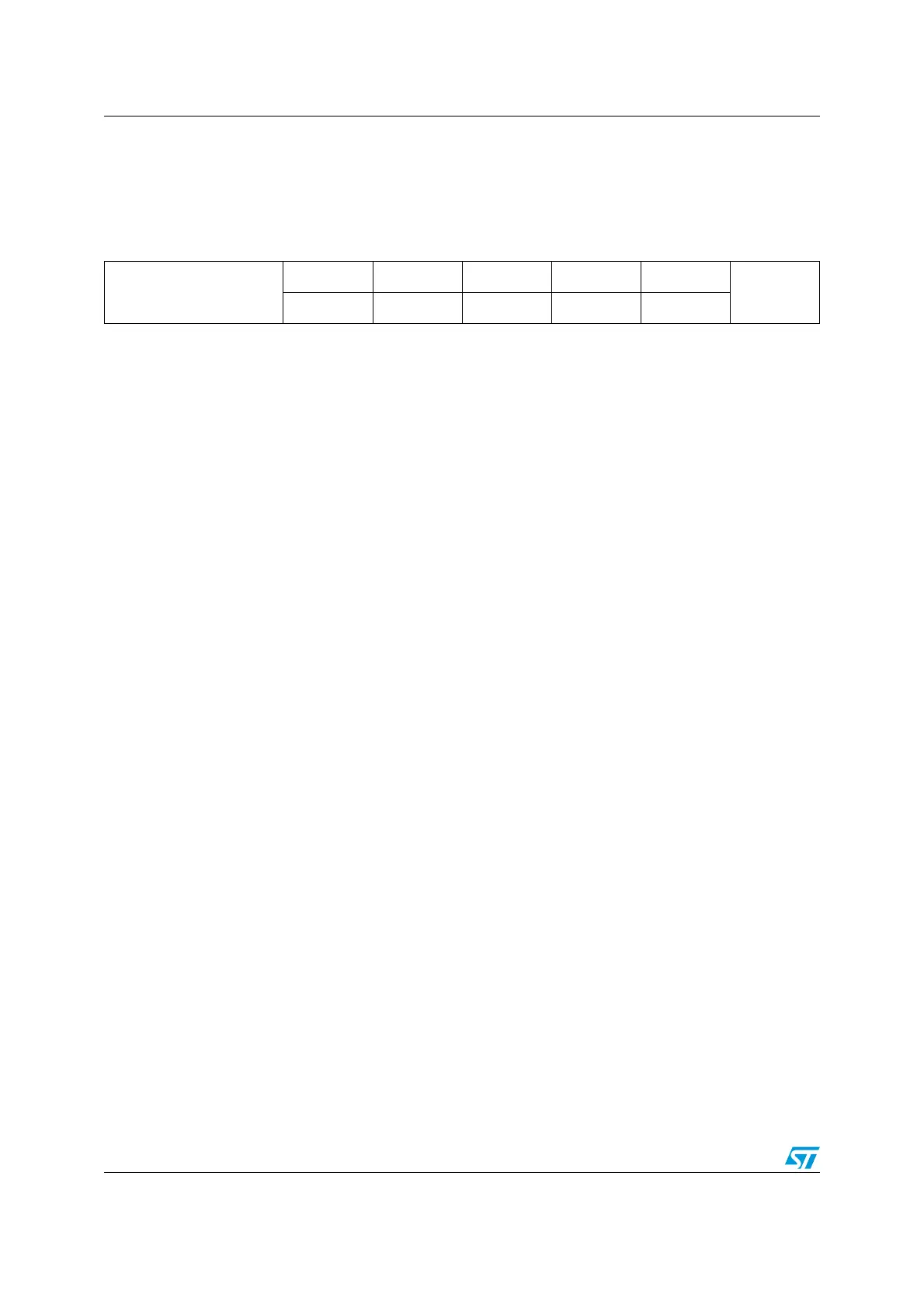

22.7.9 Control register 5 (UART_CR5)

Address offset: 0x08

Reset value: 0x00

76543210

Reserved

SCEN NACK HDSEL IRLP IREN

Reserved

r r rw rw rw

Bits 7:6 Reserved, must be kept cleared.

Bit 5 SCEN: Smartcard mode enable.

This bit is used for enabling Smartcard mode.

0: Smartcard Mode disabled

1: Smartcard Mode enabled

Note: This bit is not available for UART3.

Bit 4 NACK: Smartcard NACK enable

0: NACK transmission in case of parity error is disabled

1: NACK transmission during parity error is enabled.

Note: This bit is not available for UART3.

Bit 3 HDSEL: Half-Duplex Selection

Selection of Single-wire Half-duplex mode

0: Half duplex mode is not selected

1: Half duplex mode is selected

Note: This bit is not available for UART2 and UART3.

Bit 2 IRLP: IrDA Low Power

This bit is used for selected between normal and Low power IrDA mode

0: Normal mode

1: Low power mode

Note: This bit is not available for UART3.

Bit 1 IREN: IrDA mode Enable

This bit is set and cleared by software.

0: IrDA disabled

1: IrDA enabled

Note: This bit is not available for UART3.

Bit 0 Reserved, must be kept cleared.

Loading...

Loading...