RM0016 Inter-integrated circuit (I

2

C) interface

Doc ID 14587 Rev 8 285/449

Master transmitter

Following the address transmission and after clearing ADDR, the master sends bytes from

the DR register to the SDA line via the internal shift register.

The master waits until the first data byte is written in the DR register, (see

Figure 104Transfer sequencing EV8_1).

When the acknowledge pulse is received:

● The TXE bit is set by hardware and an interrupt is generated if the ITEVTEN and

ITBUFEN bits are set.

If TXE is set and a data byte was not written in the DR register before the end of the next

data transmission, BTF is set and the interface waits until BTF is cleared, by reading the

SR1 register and then writing to the DR register, stretching SCL low.

Closing the communication

After writing the last byte to the DR register, the STOP bit is set by software to generate a

Stop condition (see Figure 104 Transfer sequencing EV8_2). The interface goes

automatically back to slave mode (MSL bit cleared).

Note: Stop condition should be programmed during EV8_2 event, when either TXE or BTF is set.

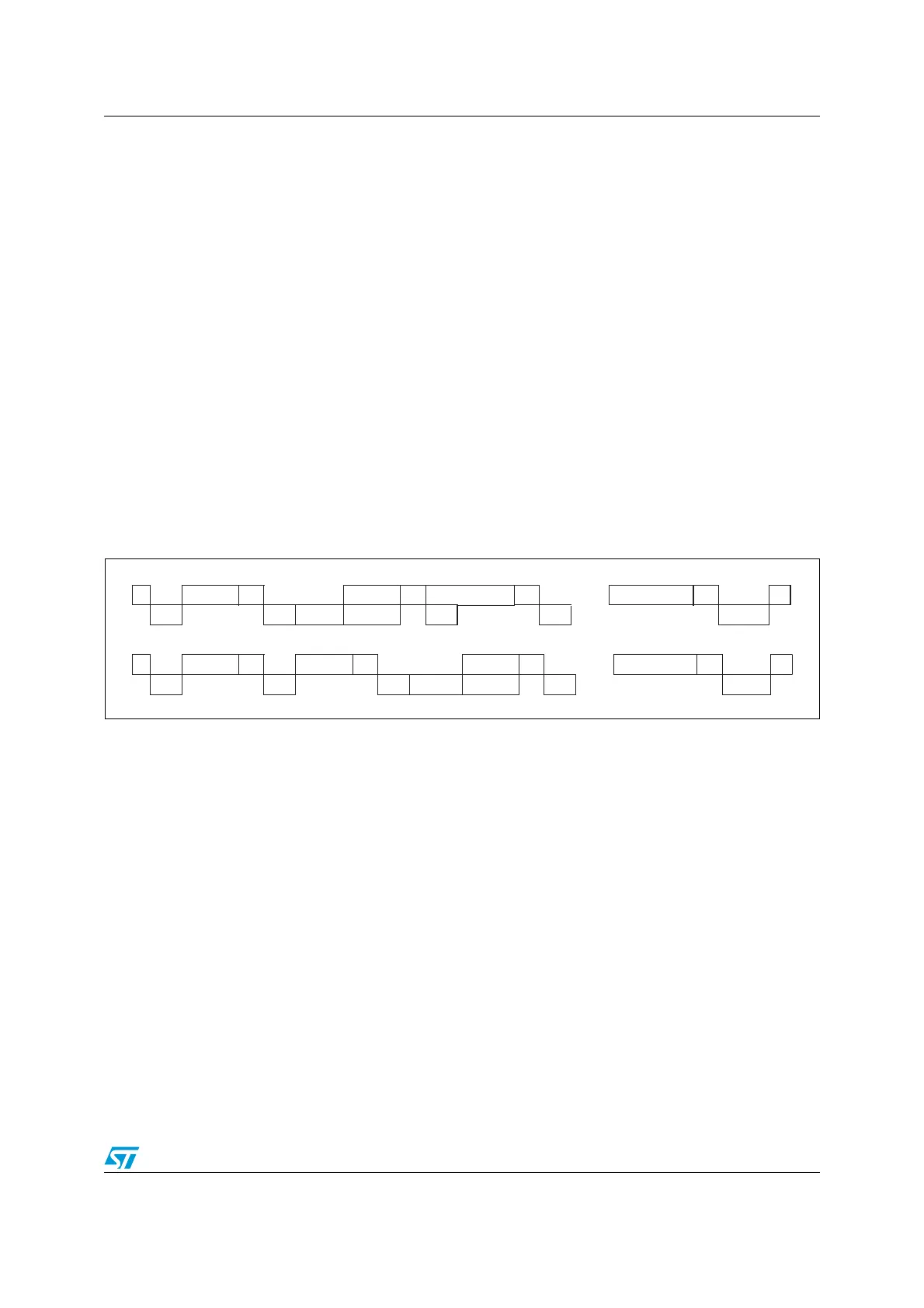

Figure 104. Transfer sequence diagram for master transmitter

1. Legend:

S= Start, S

r

= Repeated Start, P= Stop, A= Acknowledge, NA= Non-acknowledge,

EVx= Event (with interrupt if ITEVTEN=1)

EV5: SB=1, cleared by reading SR1 register followed by writing DR register with Address.

EV6: ADDR=1, cleared by reading SR1 register followed by reading SR3.

EV8_1: TXE=1, shift register empty, data register empty, write DR register.

EV8: TXE=1, shift register not empty, data register empty, cleared by writing DR register.

EV8_2: TXE=1, BTF = 1, Program STOP request. TXE and BTF are cleared by HW by stop condition

EV9: ADD10=1, cleared by reading SR1 register followed by writing DR register. See also:Note 8 on page 300

2. EV8 software sequence must be performed before the end of the current byte transfer. In case EV8 software sequence can

not be managed before the end of the current byte transfer, it is recommended to use BTF instead of TXE with the

drawback of slowing the communication.

7-bit master transmitter

10-bit master transmitter

S Address AData1A Data2A

.....

DataNA P

EV5 EV6 EV8_1 EV8 EV8 EV8 EV8_2

S Header A Address AData1A

.....

DataNA P

EV5 EV9 EV6 EV8_1 EV8 EV8 EV8_2

Ai18210

Loading...

Loading...