RM0016 Analog/digital converter (ADC)

Doc ID 14587 Rev 8 435/449

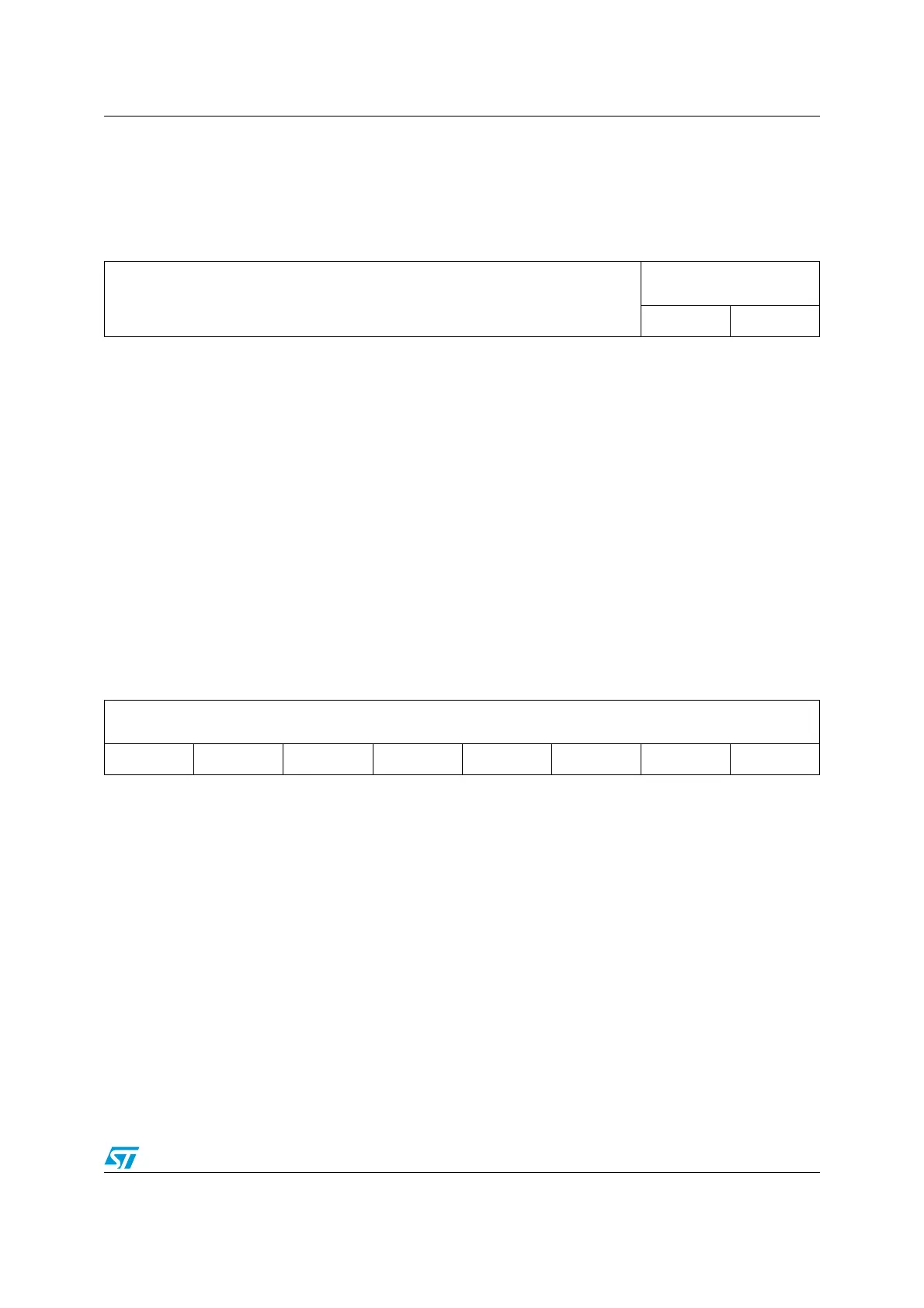

24.11.15 ADC watchdog status register high (ADC_AWSRH)

Address offset: 0x2C

Reset value: 0x00

Note: This register is not available for ADC2.

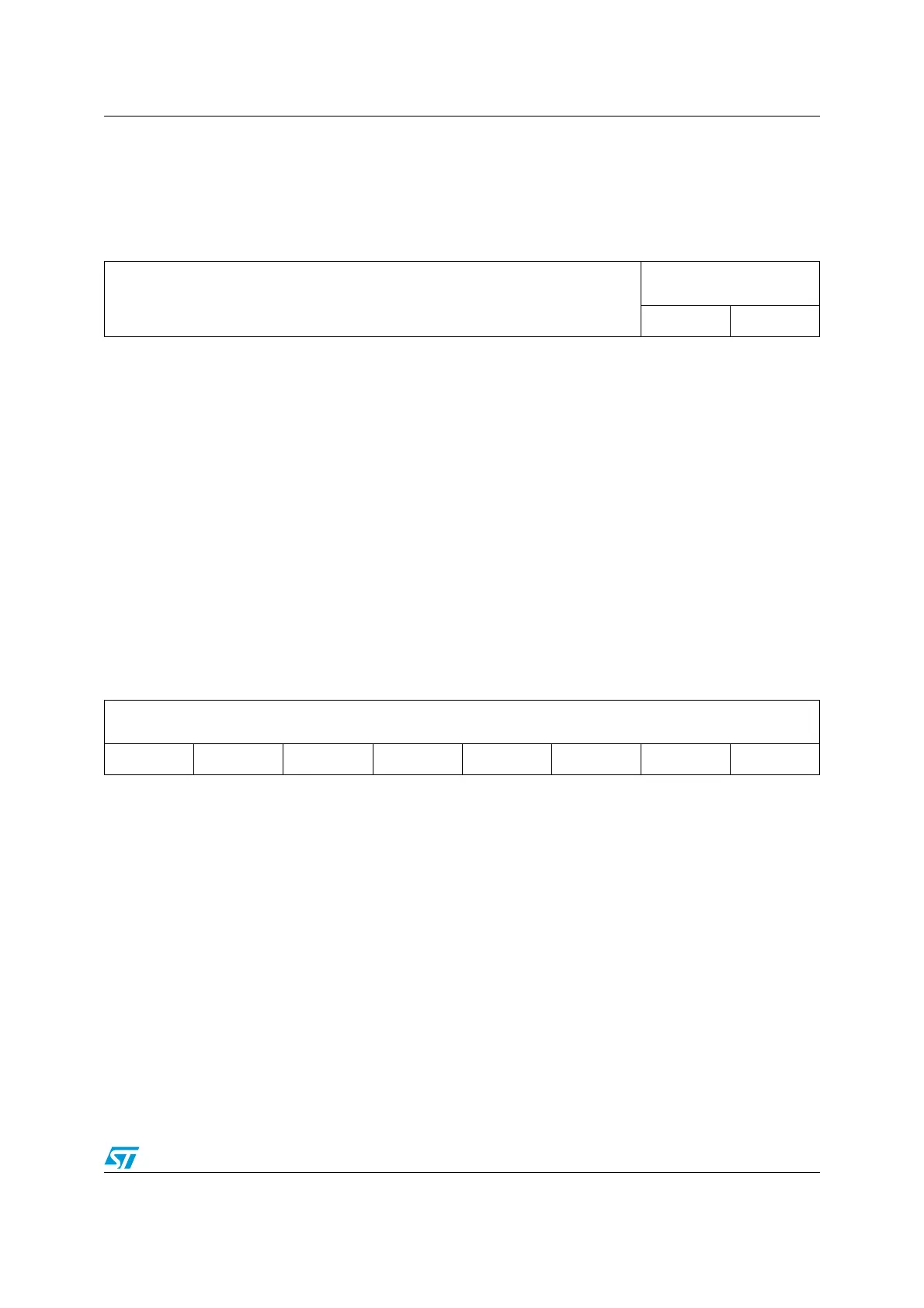

24.11.16 ADC watchdog status register low (ADC_AWSRL)

Address offset: 0x2D

Reset value: 0x00

Note: This register is not available for ADC2.

76543210

Reserved

AWS[9:8]

rc_w0 rc_w0

Bits 7:2 Reserved, must be kept cleared.

Bits 1:0 AWS[9:8] Analog watchdog status flags 9:8

These bits are set by hardware and cleared by software.

– In buffered continuous mode (DBUF=1, CONT=1) AWS flags behave

as described in Ta bl e 7 4.

– In scan mode (SCAN=1) AWS flags behave as described in Table 75.

0: No analog watchdog event in data buffer register x.

1: Analog watchdog event occurred in data buffer register x.

76543210

AWS[7:0]

rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0

Bits 7:0 AWS[7:0] Analog watchdog status flags 7:0

These bits are set by hardware and cleared by software.

– In buffered continuous mode (DBUF=1, CONT=1) AWS flags behave

as described in Ta bl e 7 4.

– In scan mode (SCAN=1) AWS flags behave as described in Table 75.

0: No analog watchdog event in data buffer register x.

1: Analog watchdog event occurred in data buffer register x.

Loading...

Loading...