16-bit advanced control timer (TIM1) RM0016

172/449 Doc ID 14587 Rev 8

Figure 70. Edge-aligned counting mode PWM mode 1 waveforms (ARR = 8)

Down-counting configuration

Down-counting is active when the DIR bit in the TIM1_CR1 register is high. Refer to Down-

counting mode on page 143

In PWM mode 1, the reference signal OCiREF is low as long as TIM1_CNT> TIM1_CCRi.

Otherwise, it becomes high. If the compare value in the TIM1_CCRi registers is greater than

the auto-reload value in the TIM1_ARR register, OCiREF is held at 1. Zero percent PWM is

not possible in this mode.

PWM center-aligned mode

Center-aligned mode is active when the CMS bits in the TIM1_CR1 register are different

from 00 (all the remaining configurations have the same effect on the OCiREF/OCi signals).

The compare flag is set when the counter counts up, down, or up and down depending on

the CMS bits configuration. The direction bit (DIR) in the TIM1_CR1 register is updated by

hardware and is read-only in this mode (refer to Center-aligned mode (up/down counting) on

page 145).

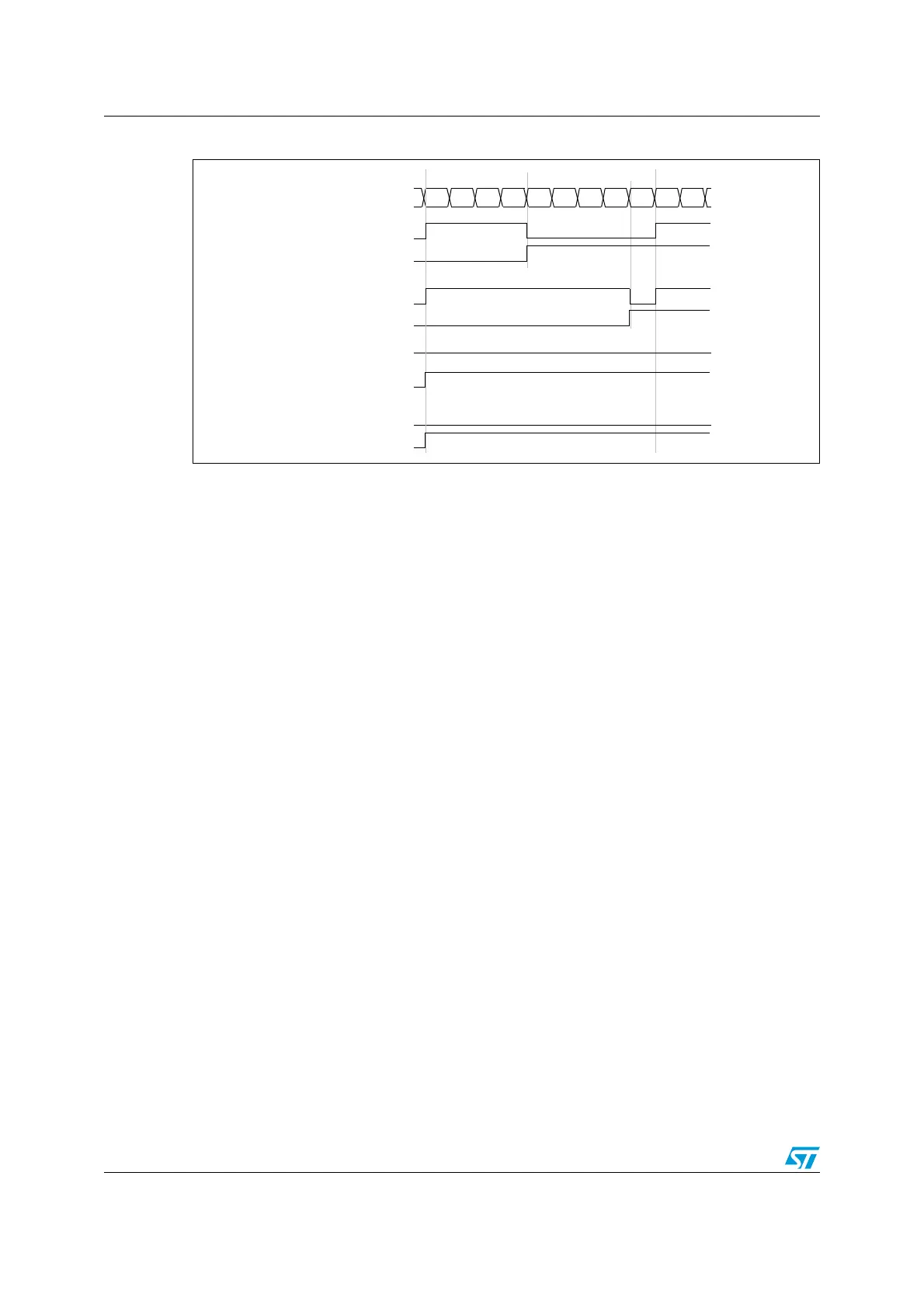

Figure 71 shows some center-aligned PWM waveforms in an example where:

● TIM1_ARR = 8,

● PWM mode is PWM mode 1

● The flag is set (arrow symbol in Figure 71) in three different cases:

– When the counter counts down (CMS = 01)

– When the counter counts up (CMS = 10)

– When the counter counts up and down (CMS = 11)

COUNTER REGISTER

‘1’

0

1234567801

‘0’

OCi

REF

CCiIF

OCi

REF

CCiIF

OCi

REF

CCiIF

OCi

REF

CCiIF

CCRx = 4

CCRx = 8

CCRx > 8

CCRx = 0

Loading...

Loading...