Auto-wakeup (AWU) RM0016

118/449 Doc ID 14587 Rev 8

12.4 AWU registers

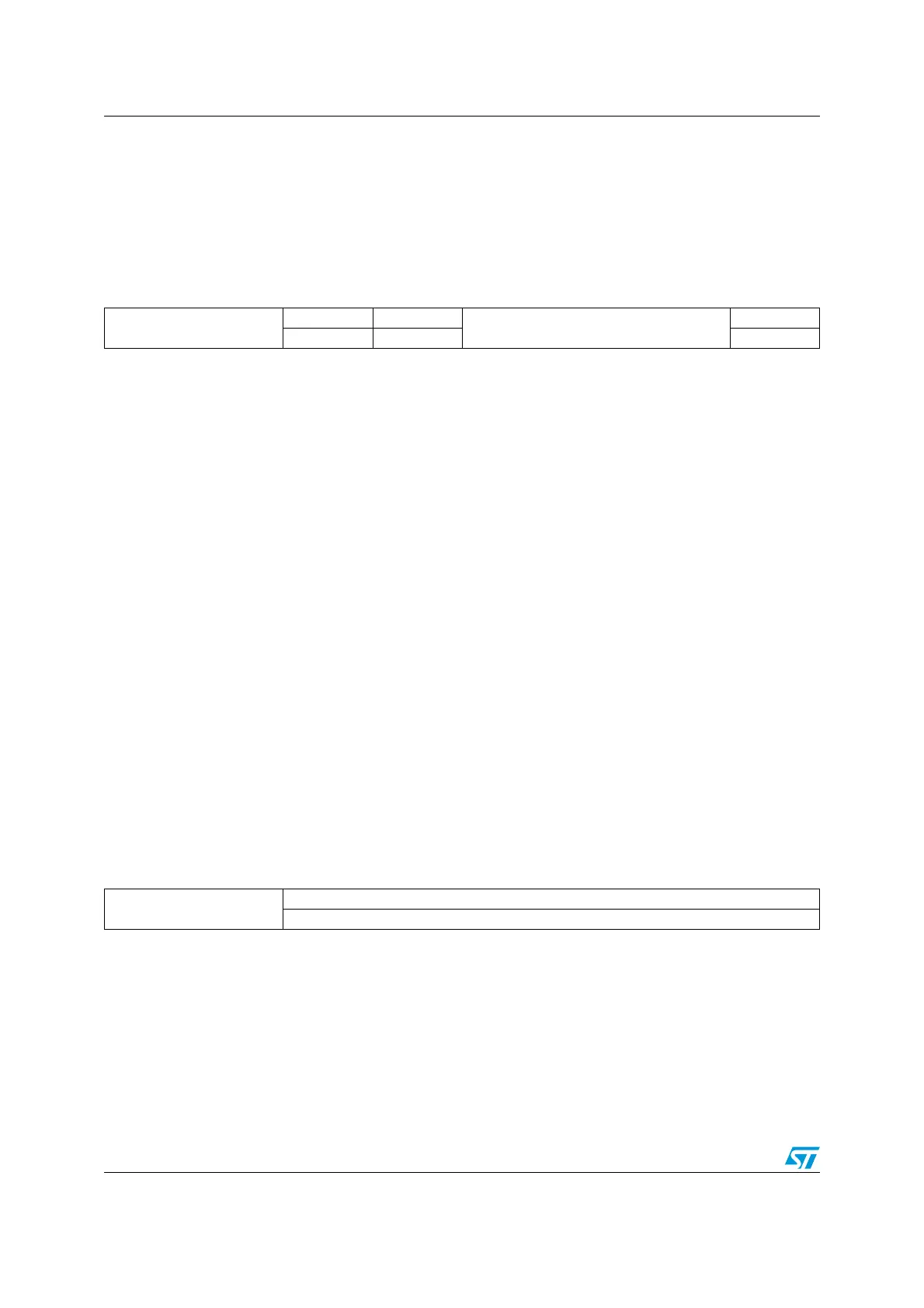

12.4.1 Control/status register (AWU_CSR)

Address offset: 0x00

Reset value: 0x00

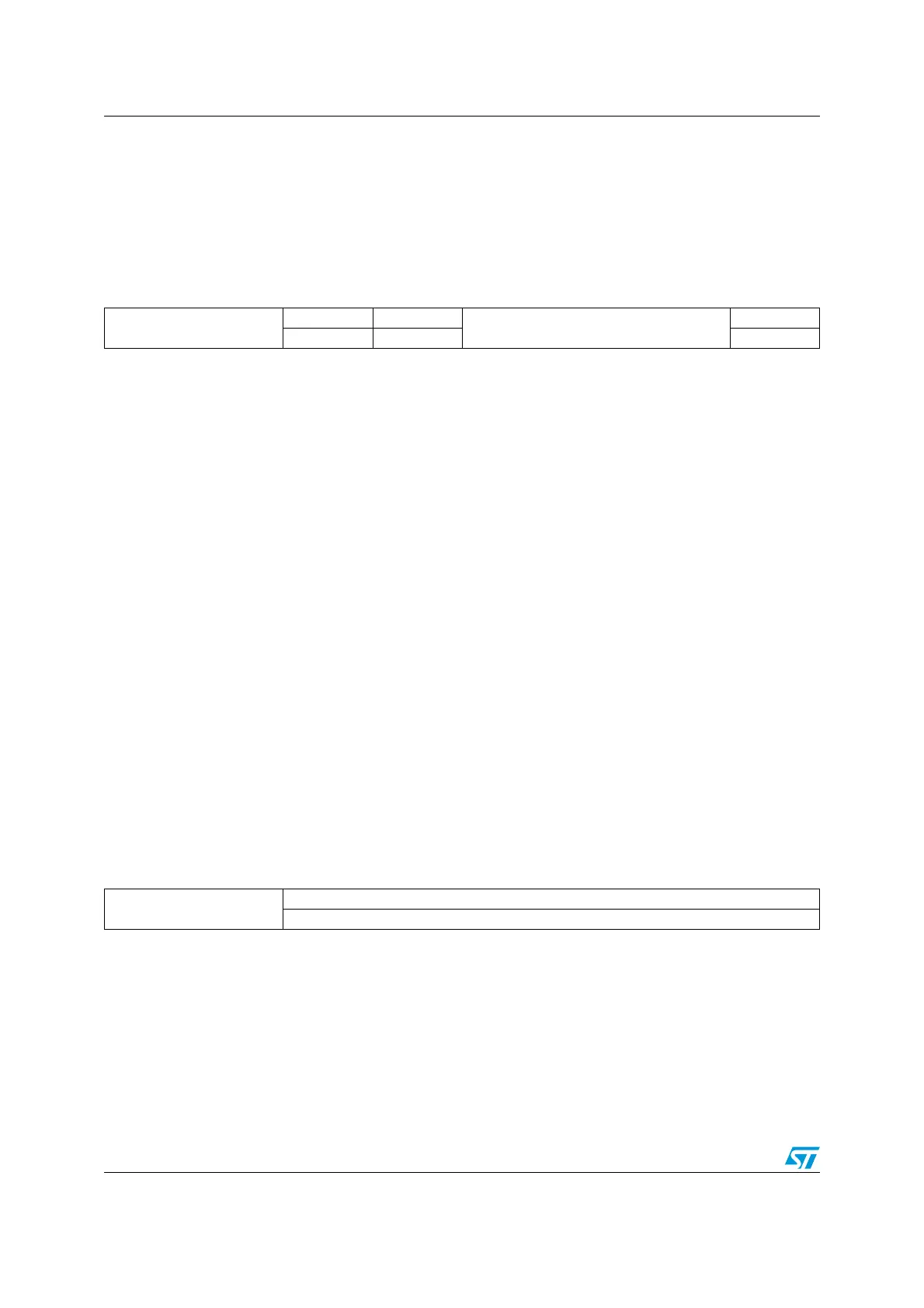

12.4.2 Asynchronous prescaler register (AWU_APR)

Address offset: 0x01

Reset value: 0x3F

76543210

Reserved

AWUF AWUEN

Reserved

MSR

rc_r rw rw

Bits 7:6 Reserved

Bit 5 AWUF: Auto-wakeup flag

This bit is set by hardware when the AWU module generates an interrupt and cleared by reading the

AWU_CSR register. Writing to this bit does not change its value.

0: No AWU interrupt occurred

1: AWU interrupt occurred

Bit 4 AWUEN: Auto-wakeup enable

This bit is set and cleared by software. It enables the auto-wakeup feature. If the microcontroller enters

Active-halt or Wait mode, the AWU feature wakes up the microcontroller after a programmable time

delay.

0: AWU (Auto-wakeup) disabled

1: AWU (Auto-wakeup) enabled

Bits 3:1 Reserved

Bit 0 MSR: Measurement enable

This bit connects the f

LS

clock to a timer input capture. This allows the timer to be used to measure the

LS frequency (f

LS

).

0: Measurement disabled

1: Measurement enabled

Note: Refer to the datasheet for information on which timer input capture can be connected to the LSI

clock in the specific product).

76543210

Reserved

APR[5:0]

rw

Bits 7:6 Reserved

Bits 5:0 APR[5:0]: Asynchronous prescaler divider

These bits are written by software to select the prescaler divider (APR

DIV

) feeding the counter clock.

0x00: APR

DIV

= 2 0x0E: APR

DIV

= 16

0x01: APR

DIV

= 3 0x0F: APR

DIV

= 17

... ...

0x06: APR

DIV

= 8 0x3E: APR

DIV

= 64

Note: This register must not be kept at its reset value (0x3F)

Loading...

Loading...