RM0016 Serial peripheral interface (SPI)

Doc ID 14587 Rev 8 263/449

Transmit-only procedure (BDM = 0 RXONLY = 0)

In this mode, the procedure can be reduced as described below and the BSY bit can be

used to wait until the effective completion of the transmission (see Figure 94 and Figure 95):

1. Enable the SPI by setting the SPE bit

2. Write the first data to send in the SPI_DR register (this clears the TXE bit).

3. Wait until TXE = 1 and write the next data to be transmitted. Repeat this step for each

data to be transmitted.

4. After writing the last data in the SPI_DR register, wait until TXE = 1 and then wait until

BSY=0 which indicates that the transmission of the last data is complete.

This procedure can be also implemented using dedicated interrupt subroutines launched at

each rising edge of TXE flag.

Note: 1 In master mode, during discontinuous communications, there is a 2 CPU clock period delay

between the write operation to SPI_DR and the BSY bit setting. As a consequence, in

transmit-only mode, it is mandatory to wait first until TXE is set and then until BSY is reset

after having written the last data.

2 After transmitting two data in transmit-only mode, the OVR flag is set in the SPI_SR register

since the received data are never read.

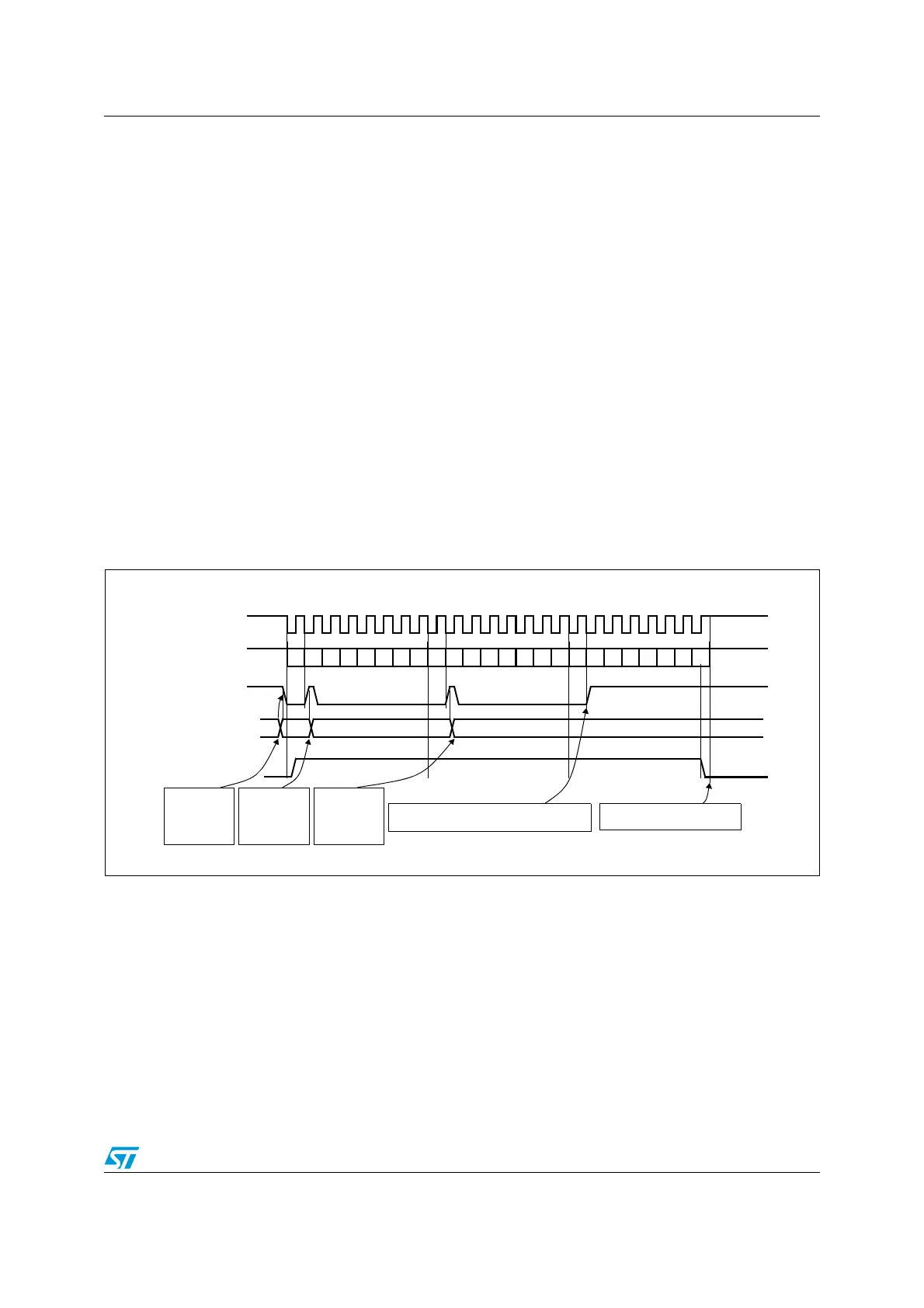

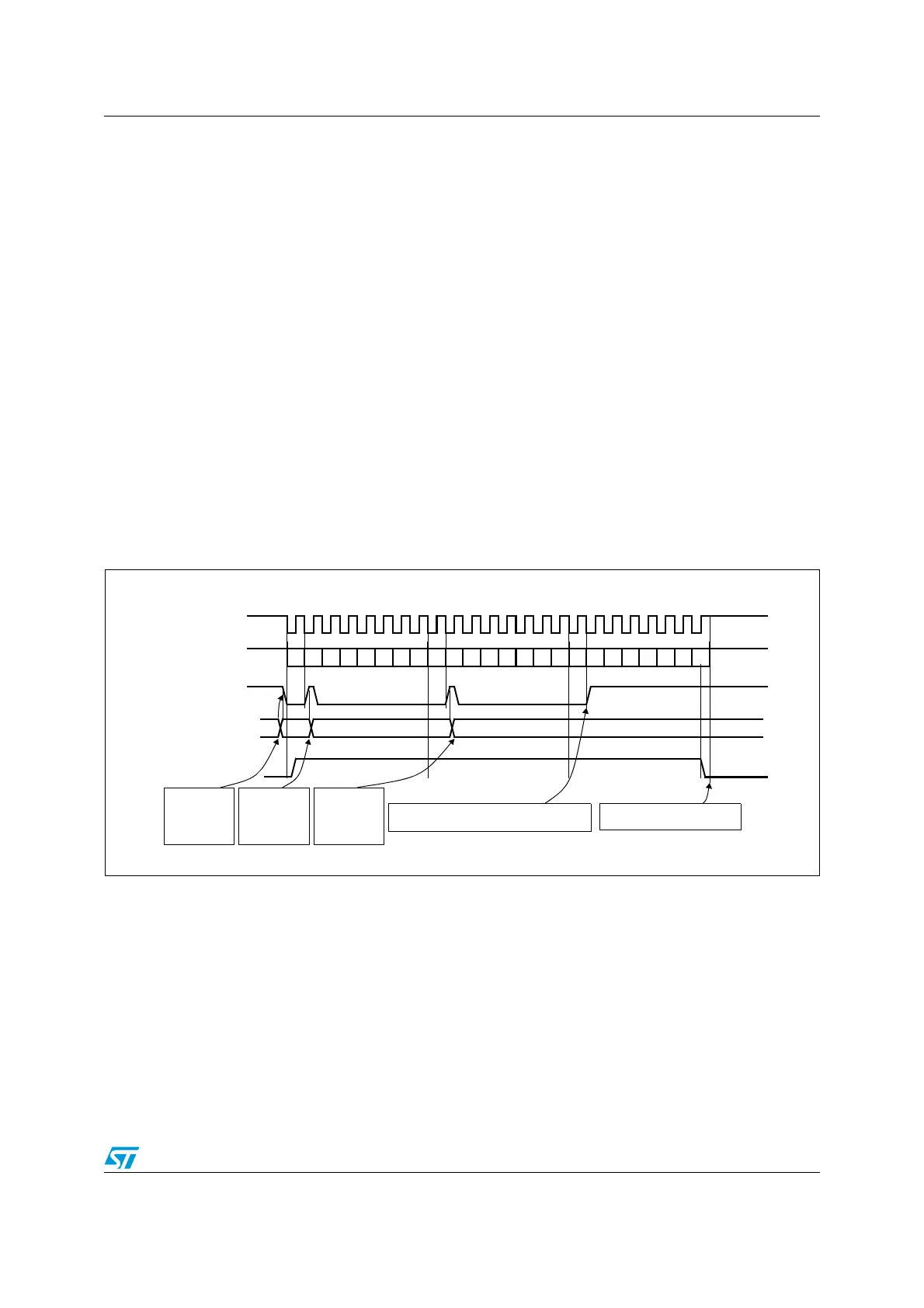

Figure 96. TXE/BSY in master transmit-only mode

(BDM = 0 and RXONLY = 0). Case of continuous transfers

0xF1

Tx Buffer

TXE flag

0xF2

BSY flag

0xF3

software writes

0xF1 in SPI_DR

software waits

until TXE=1 and

writes 0xF2 in

SPI_DR

set by hw

cleared by sw

set by hw

cleared by sw

set by hw

set by hw

SCK

reset by hw

Example in master mode with CPOL=1, CPHA=1

(write SPI_DR)

MISO/MOSI (out)

DATA 1 = 0xF1 DATA 2 = 0xF2

DATA 3 = 0xF3

software waits

until TXE=1 and

writes 0xF3 in

SPI_DR

software waits until BSY=0software waits until TXE=1

b0 b1 b2 b3 b4 b5 b6 b7 b0 b1 b2 b3 b4 b5 b6 b7

b0 b1 b2 b3 b4 b5 b6 b7

Loading...

Loading...