Controller area network (beCAN) RM0016

388/449 Doc ID 14587 Rev 8

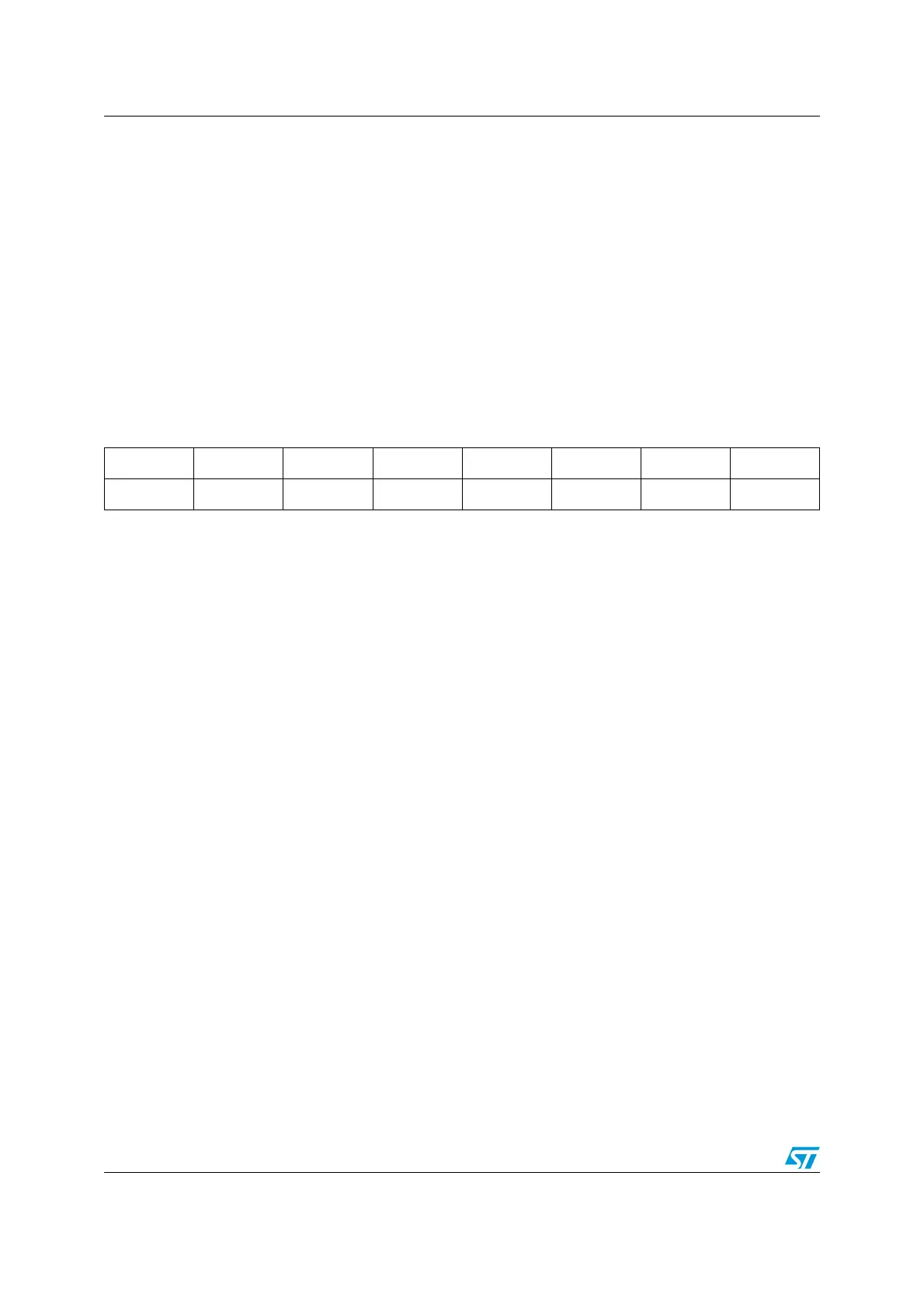

23.11.4 CAN transmit priority register (CAN_TPR)

Address offset: 0x03

Reset value: 0x0C

Bit 1 RQCP1 Request Completed for Mailbox 1

This bit is set by hardware to signal that the last request for mailbox 1 has been completed. The

request could be a transmit or an abort request.

This bit is cleared by software writing 1.

Bit 0 RQCP0 Request Completed for Mailbox 0

This bit is set by hardware to signal that the last request for mailbox 0 has been completed. The

request could be a transmit or an abort request.

This bit is cleared by software writing 1.

76543210

LOW2 LOW1 LOW0 TME2 TME1 TME0 CODE1 CODE0

rrrrrrrr

Bit 7 LOW2 Lowest Priority Flag for Mailbox 2

This bit is set by hardware when more than one mailbox is pending for transmission and mailbox 2

has the lowest priority.

Note: It is set to zero when only one mailbox is pending.

Bit 6 LOW1 Lowest Priority Flag for Mailbox 1

This bit is set by hardware when more than one mailbox is pending for transmission and mailbox 1

has the lowest priority.

Note: It is set to zero when only one mailbox is pending.

Bit 5 LOW0 Lowest Priority Flag for Mailbox 0

This bit is set by hardware when more than one mailbox is pending for transmission and mailbox 0

has the lowest priority.

Note: It is set to zero when only one mailbox is pending.

Bit 4 TME2 Transmit Mailbox 2 Empty

This bit is set by hardware when no transmit request is pending for mailbox 2.

Note: This bit is reserved, forced to 0 by hardware in ST7 beCAN compatibility mode (TXM2E bit = 0

in CAN_DGR register).

Bit 3 TME1 Transmit Mailbox 1 Empty

This bit is set by hardware when no transmit request is pending for mailbox 1.

Bit 2 TME0 Transmit Mailbox 0 Empty

This bit is set by hardware when no transmit request is pending for mailbox 0.

Bits 1:0 CODE[1:0] Mailbox Code

When at least one transmit mailbox is free, this field contains the number of the next free transmit

mailbox.

When all transmit mailboxes are pending, this field contains the number of the transmit mailbox with

the lowest priority.

Note: CODE1 is always 0 in ST7 beCAN compatibility mode (TXM2E bit = 0 in CAN_DGR register).

Loading...

Loading...