RM0016 Analog/digital converter (ADC)

Doc ID 14587 Rev 8 421/449

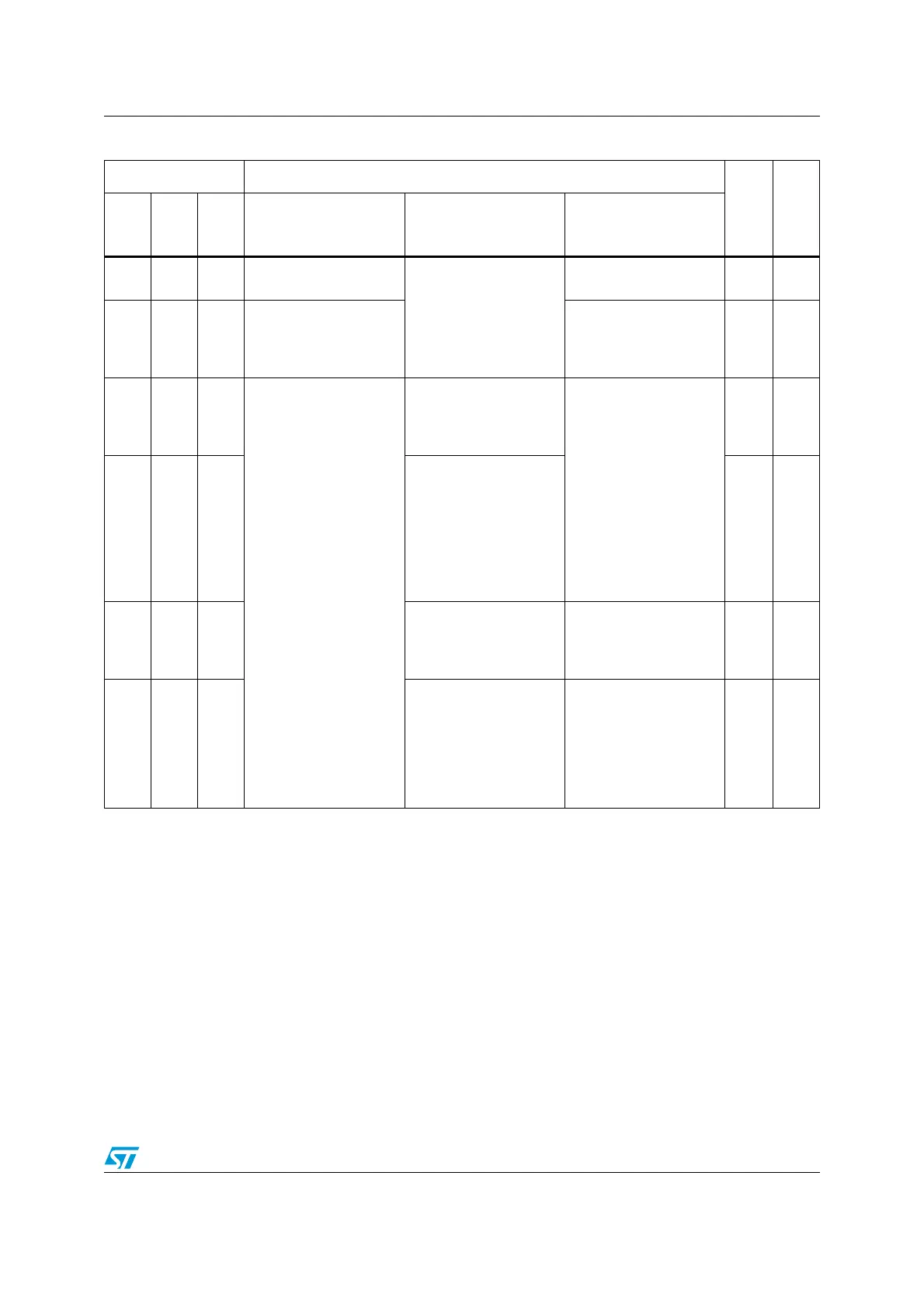

Table 74. ADC interrupts in buffered continuous mode (ADC1)

Enable bits Status flags

Exit

from

Wait

Exit

from

Halt

AWENx

AWDIE

EOCIE

AWSx AWD EOC

0

Don’t

care

0 0

0

The flag is set at the end

of BSIZE conversions

No No

0

Don’t

care

1 0

The flag is set at the end

of BSIZE conversions

and an interrupt is

generated.

Yes No

1 0 0

Flag is set if conversion

on buffer ”x” crosses the

thresholds programmed

in the ADC_HTR and

ADC_LTR registers

The flag is set at the end

of BSIZE conversions if

at least one of the

AWSx bits is set

The flag is set at the end

of BSIZE conversions

(Data Buffer Full)

No No

1 1 0

The flag is set and an

interrupt is generated at

the end of BSIZE

conversions if at least

one of the AWSx bits is

set. Continuous

conversion is not

stopped.

Yes No

1 0 1

The flag is set at the end

of BSIZE conversions if

at least one of the

AWSx bits is set

The flag is set at the end

of BSIZE conversions

and an interrupt is

generated.

Yes No

1 1 1

The flag is set

immediately as soon as

one of the AWSx bits is

set. In interrupt is

generated and

continuous conversion

is stopped.

The flag is set at the end

of BSIZE conversions

and an interrupt is

generated.

Ye s N o

Loading...

Loading...