Window watchdog (WWDG) RM0016

130/449 Doc ID 14587 Rev 8

15.6 Hardware watchdog option

If hardware watchdog is selected by option byte, the watchdog is always active and the

WDGA bit in the WWDG_CR register is not used. Refer to the option byte description in the

datasheet.

15.7 Using Halt mode with the WWDG (WWDGHALT option)

The following recommendation applies if Halt mode is used when the watchdog is enabled.

Before executing the HALT instruction, refresh the WDG counter, to avoid an unexpected

WWDG reset immediately after waking up the microcontroller.

15.8 WWDG interrupts

None.

15.9 WWDG registers

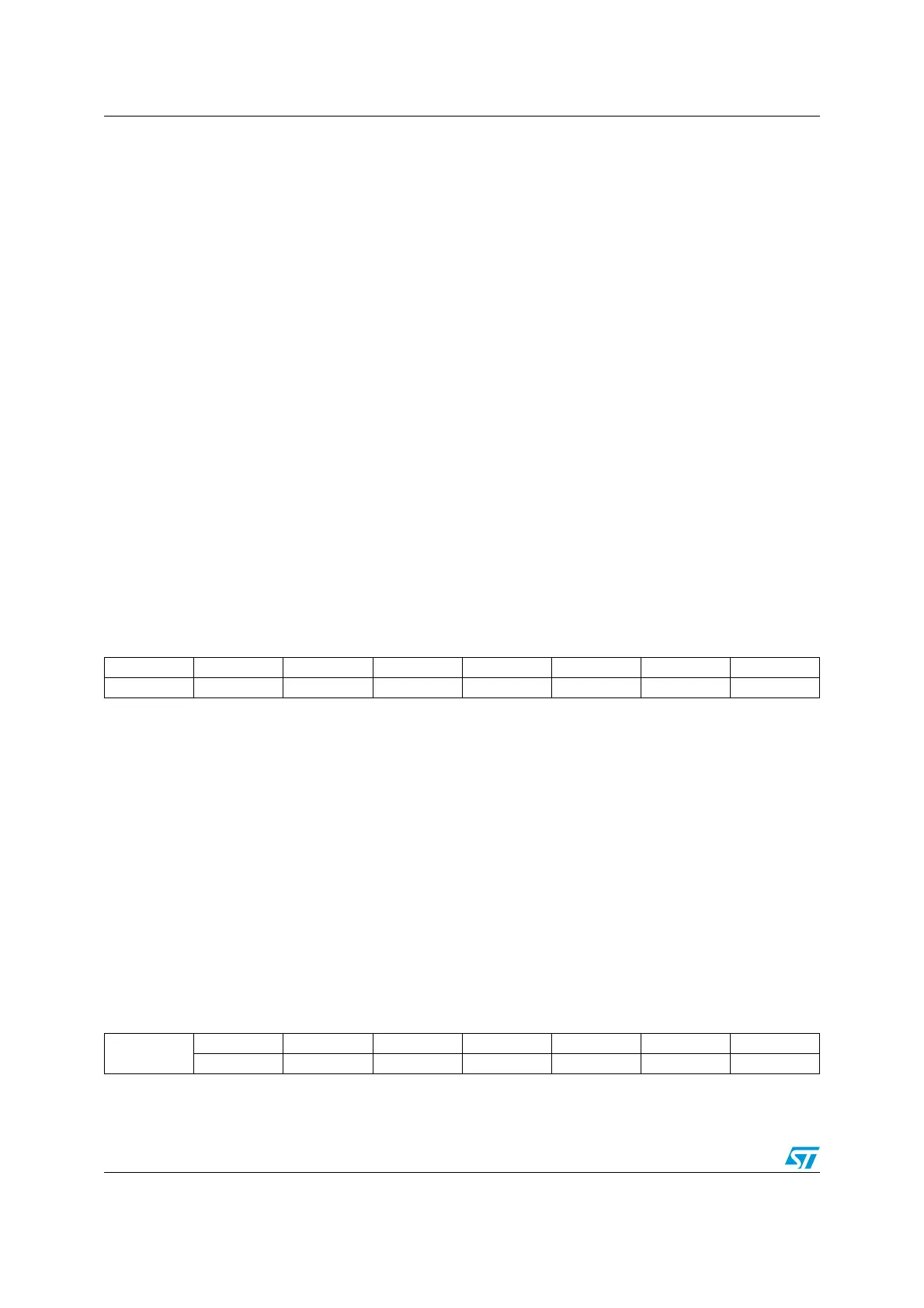

15.9.1 Control register (WWDG_CR)

Address offset: 0x00

Reset value: 0x7F

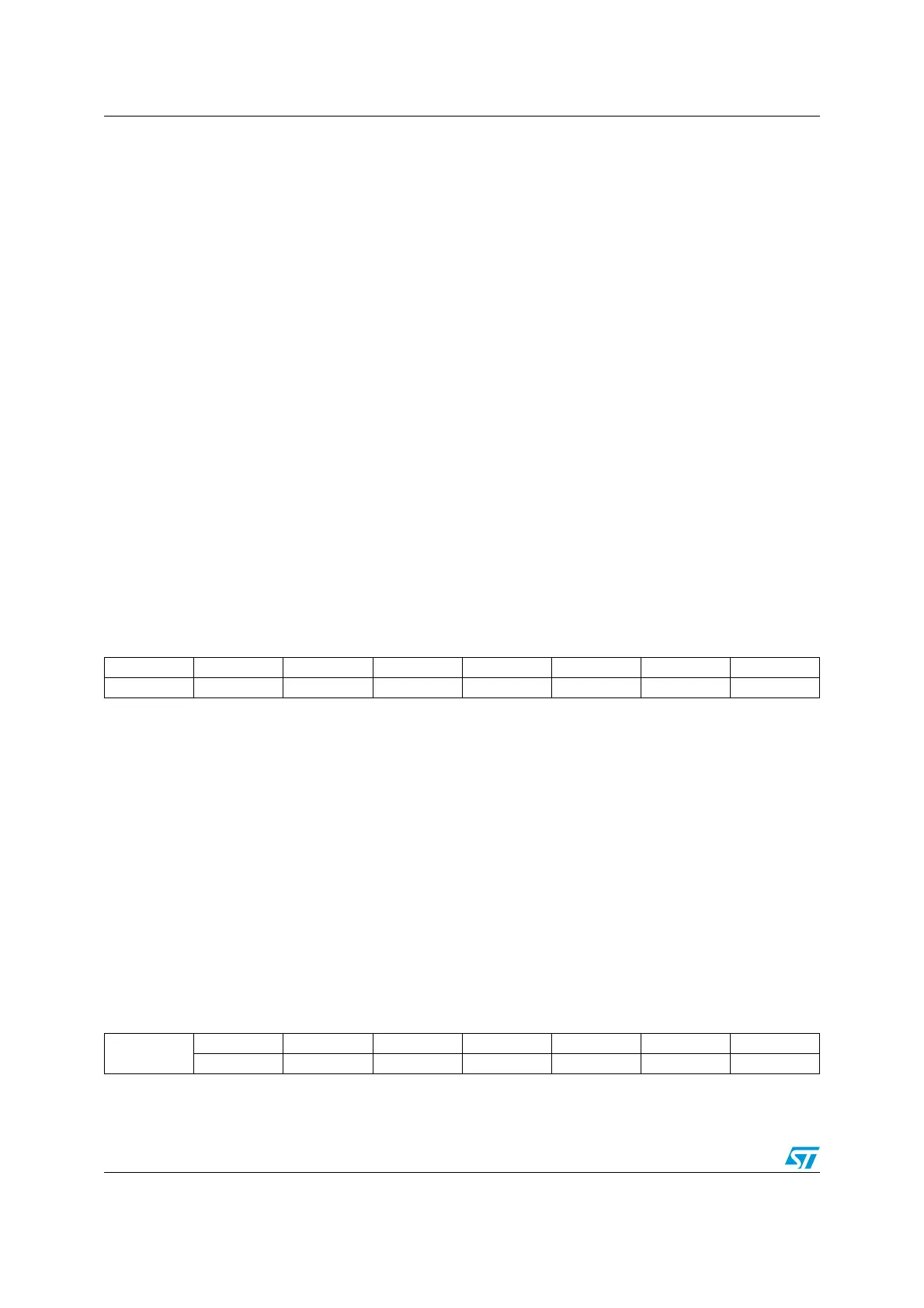

15.9.2 Window register (WWDG_WR)

Address offset: 0x01

Reset value: 0x7F

76543210

WDGA T6 T5 T4 T3 T2 T1 T0

rs rw rw rw rw rw rw rw

Bit 7 WDGA: Activation bit

(1)

This bit is set by software and only cleared by hardware after a reset. When WDGA = 1, the watchdog

can generate a reset.

0: Watchdog disabled

1: Watchdog enabled

Bits 6:0 T[6:0]: 7-bit counter (MSB to LSB)

These bits contain the value of the watchdog counter. It is decremented every 12288 f

CPU

cycles

(approximately). A reset is produced when it rolls over from 0x40 to 0x3F (T6 becomes cleared).

1. This bit is not used if the hardware watchdog option is enabled by option byte.

76543210

Reserved

W6 W5 W4 W3 W2 W1 W0

rw rw rw rw rw rw rw

Bit 7 Reserved

Loading...

Loading...