RM0016 Beeper (BEEP)

Doc ID 14587 Rev 8 121/449

13.2.2 Beeper calibration

This procedure can be used to calibrate the LS 128 kHz clock in order to reach the standard

frequency output, 1 kHz, 2 kHz or 4 kHz.

Use the following procedure:

1. Measure the LSI clock frequency (refer to Section 12.3.3: LSI clock frequency

measurement above).

2. Calculate the BEEP

DIV

value as follows, where A and x are the integer and fractional

part of f

LS

/8 (in kHz):

BEEP

DIV

= A-2 when x is less than or equal to A/(1+2*A), else

BEEP

DIV

= A-1

3. Write the resulting BEEP

DIV

value in the BEEPDIV[4:0] bits in the Beeper control/status

register (BEEP_CSR).

13.3 Beeper registers

13.3.1 Beeper control/status register (BEEP_CSR)

Address offset: 0x00

Reset value: 0x1F

13.3.2 Beeper register map and reset values

76543210

BEEPSEL[1:0] BEEPEN BEEPDIV[4:0]

rw rw rw

Bits 7:6 BEEPSEL[1:0]: Beep selection

These bits are set and cleared by software to select 1, 2 or 4 kHz beep output when calibration is

done.

00: f

LS

/(8 x BEEP

DIV

) kHz output

01: f

LS

/(4 x BEEP

DIV

) kHz output

1x: f

LS

/(2 x BEEP

DIV

) kHz output

Bit 5 BEEPEN: Beep enable

This bit is set and cleared by software to enable the beep feature.

0: Beep disabled

1: Beep enabled

Bits 4:0 BEEPDIV[4:0]: Beep prescaler divider

These bits are set and cleared by software to define the Beeper prescaler dividing factor BEEP

DIV

.

0x00: BEEP

DIV

= 2 0x0E: BEEP

DIV

= 16

0x01: BEEP

DIV

= 3 0x0F: BEEP

DIV

= 17

... 0x1E: BEEP

DIV

= 32

Note: This register must not be kept at its reset value (0x1F)

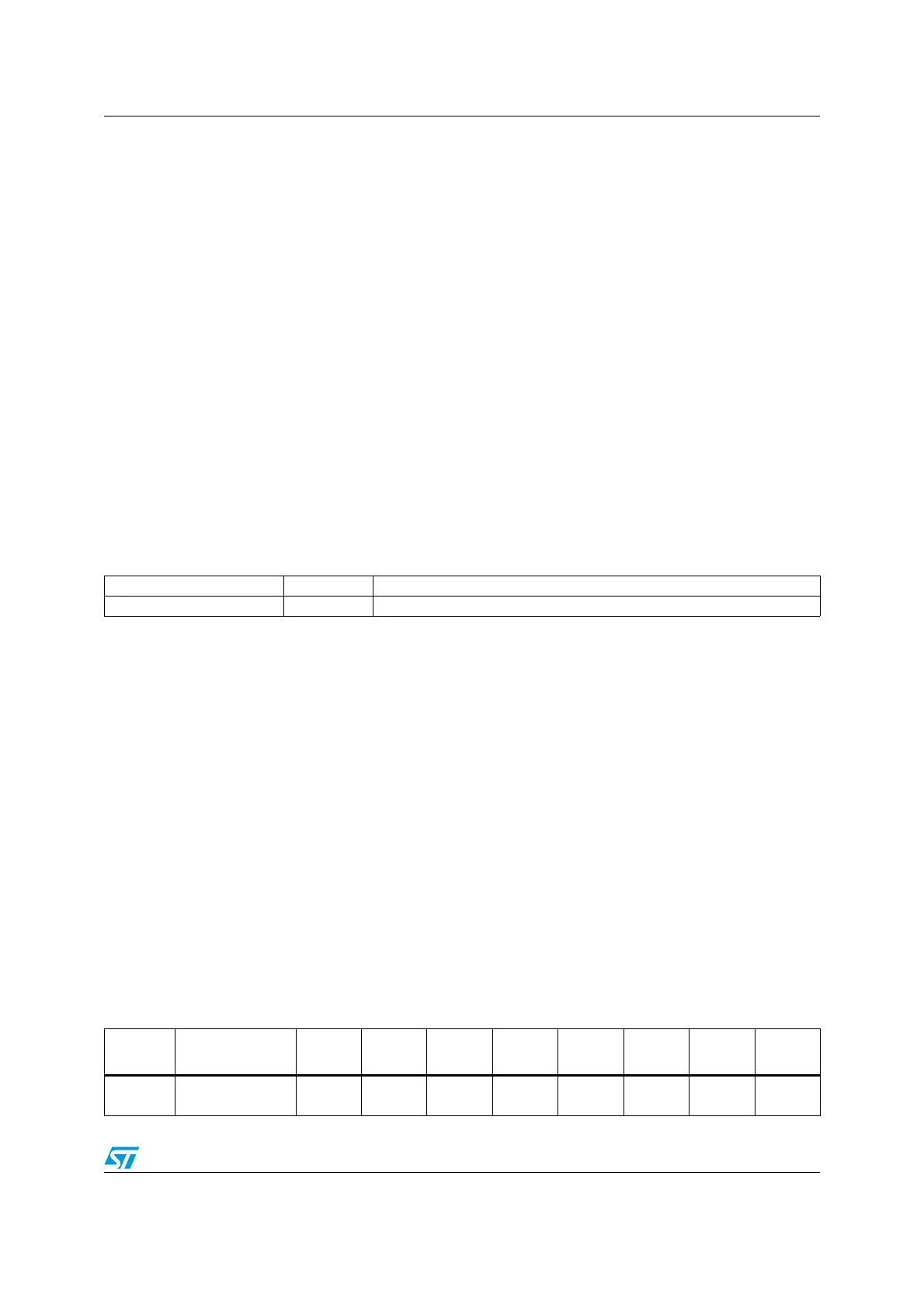

Table 27. Beeper register map

Address

offset

Register name76543210

0x00 BEEP_CSR

BEEP

SEL20

BEEP

SEL10

BEEPE

N0

BEEP

DIV41

BEEP

DIV31

BEEP

DIV21

BEEP

DIV11

BEEP

DIV01

Loading...

Loading...