Analog/digital converter (ADC) RM0016

420/449 Doc ID 14587 Rev 8

24.6 ADC low power modes

The ADC does not have the capability to wake the device from Active-halt or Halt mode.

24.7 ADC interrupts

The ADC interrupt control bits are summarized in Tabl e 7 3, Ta bl e 7 4 and Ta bl e 7 5

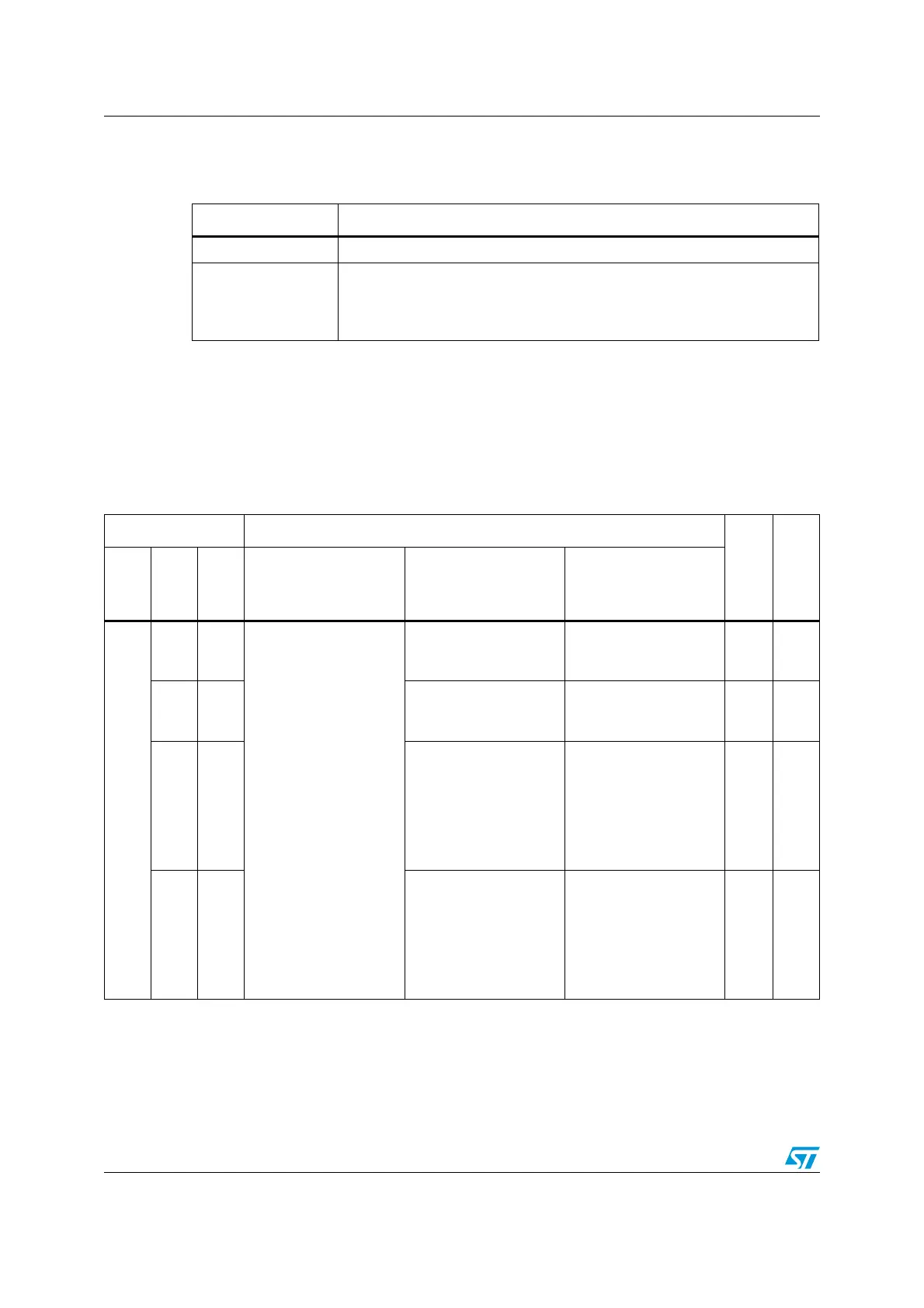

Table 72. Low power modes

Mode Description

Wait No effect on ADC

Halt/

Active-halt

In devices with extended features, the ADC is automatically switched off

before entering Halt/Active-halt mode. After waking up from Active-halt, the

ADON bit must be set by software to power on the ADC, and a delay of 7 µs

is needed before starting a new conversion.

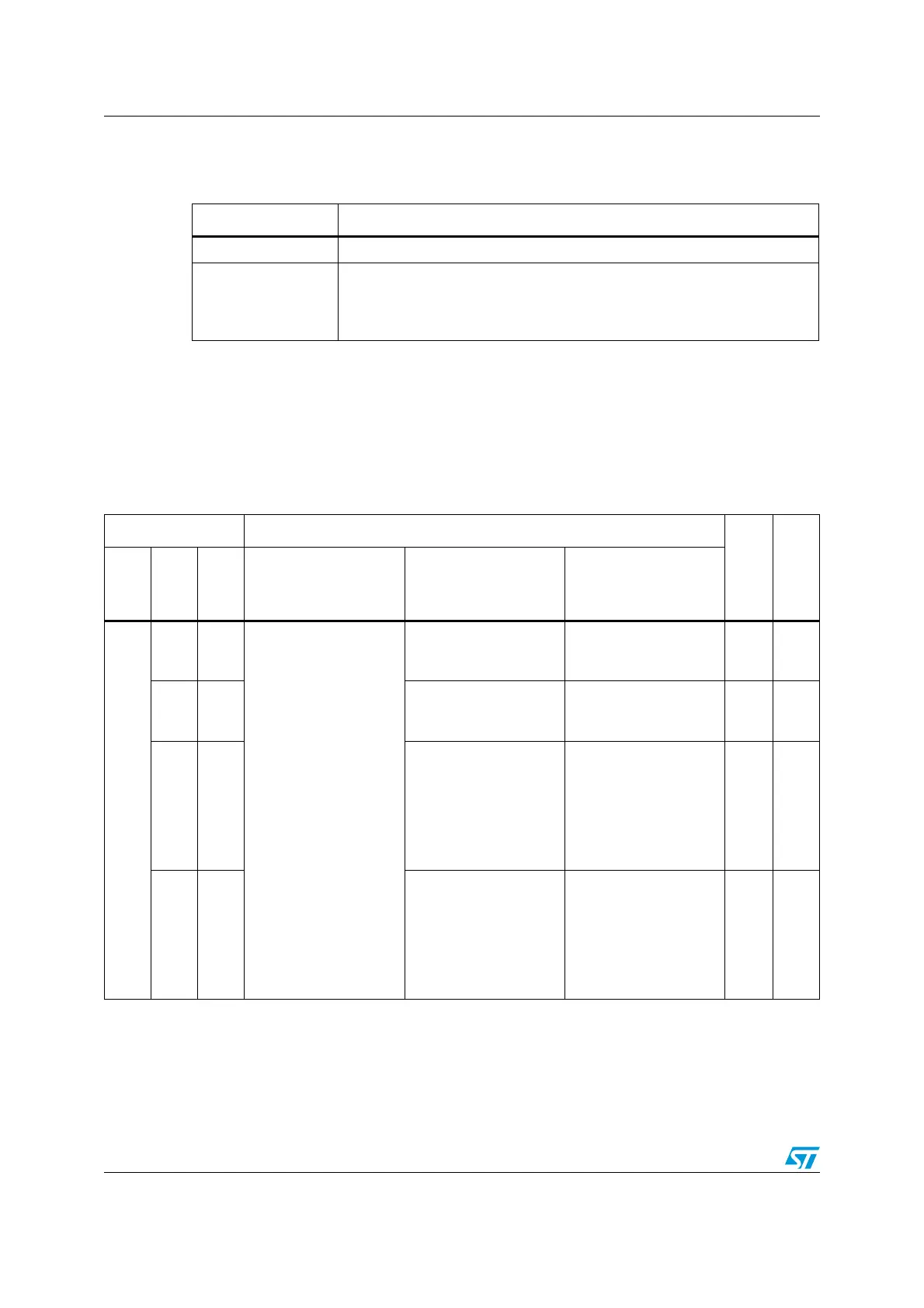

Table 73. ADC Interrupts in single and non-buffered continuous mode (ADC1 and ADC2)

(1)

Enable bits Status flags

Exit

from

Wait

Exit

from

Halt

AWDENx

AWDIE

EOCIE

AWSx AWDG EOC

Don’t

care

0 0

Don’t care

Flag is set if the channel

crosses the

programmed thresholds.

Flag is set at the end of

each conversion.

No No

0 1

Flag is set if the channel

crosses the

programmed thresholds.

Flag is set at the end of

each conversion and an

interrupt is generated.

Ye s N o

1 0

Flag is set if the channel

crosses the

programmed thresholds.

An interrupt is

generated but

continuous conversion

is not stopped.

Flag is set at the end of

each conversion.

Ye s N o

1 1

Flag is set if the channel

crosses the

programmed thresholds.

An interrupt is

generated but

continuous conversion

is not stopped.

Flag is set at the end of

each conversion and an

interrupt is generated.

Ye s n o

1. BSIZE = Data buffer size (8 or 10 depending on the product).

Loading...

Loading...