Serial peripheral interface (SPI) RM0016

274/449 Doc ID 14587 Rev 8

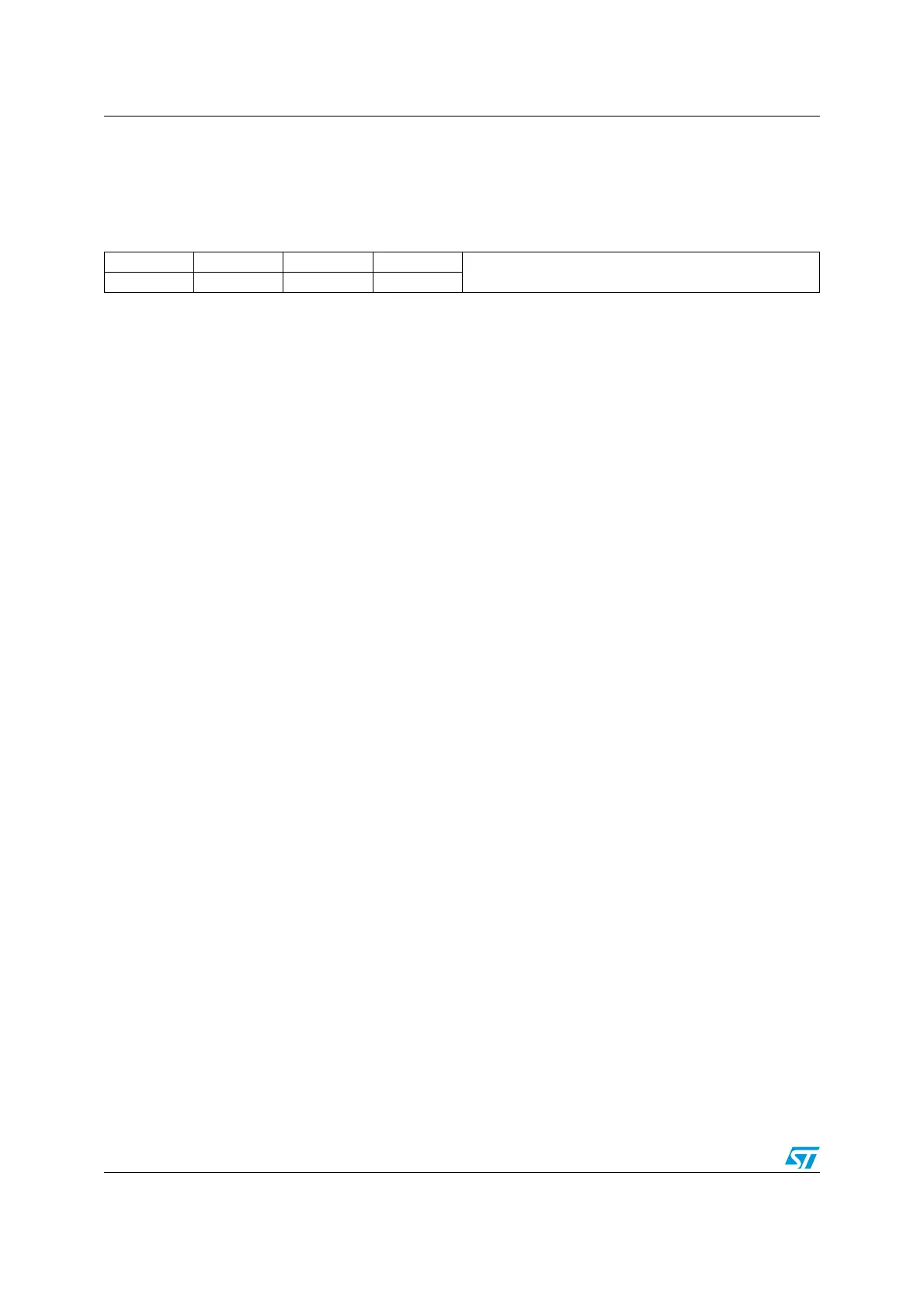

20.4.3 SPI interrupt control register (SPI_ICR)

Address offset: 0x02

Reset value: 0x00

76543210

TXIE RXIE ERRIE WKIE

Reserved

rw rw rw rw

Bit 7 TXIE: Tx buffer empty interrupt enable

0: TXE interrupt masked

1: TXE interrupt not masked. This allows an interrupt request to be generated when the TXE flag is

set.

Bit 6 RXIE: RX buffer not empty interrupt enable

0: RXNE interrupt masked

1: RXNE interrupt not masked. This allows an interrupt request to be generated when the RXNE flag

is set.

Bit 5 ERRIE: Error interrupt enable

0: Error interrupt is masked

1: Error interrupt is enabled. This allows an interrupt request to be generated when an error

condition occurs (CRCERR, OVR, MODF)

Bit 4 WKIE: Wakeup interrupt enable

0: wakeup interrupt masked

1: wakeup interrupt enabled. This allows an interrupt request to be generated when the WKUP flag

is set.

Bits 3:0 Reserved

Loading...

Loading...