RM0016 8-bit basic timer (TIM4, TIM6)

Doc ID 14587 Rev 8 251/449

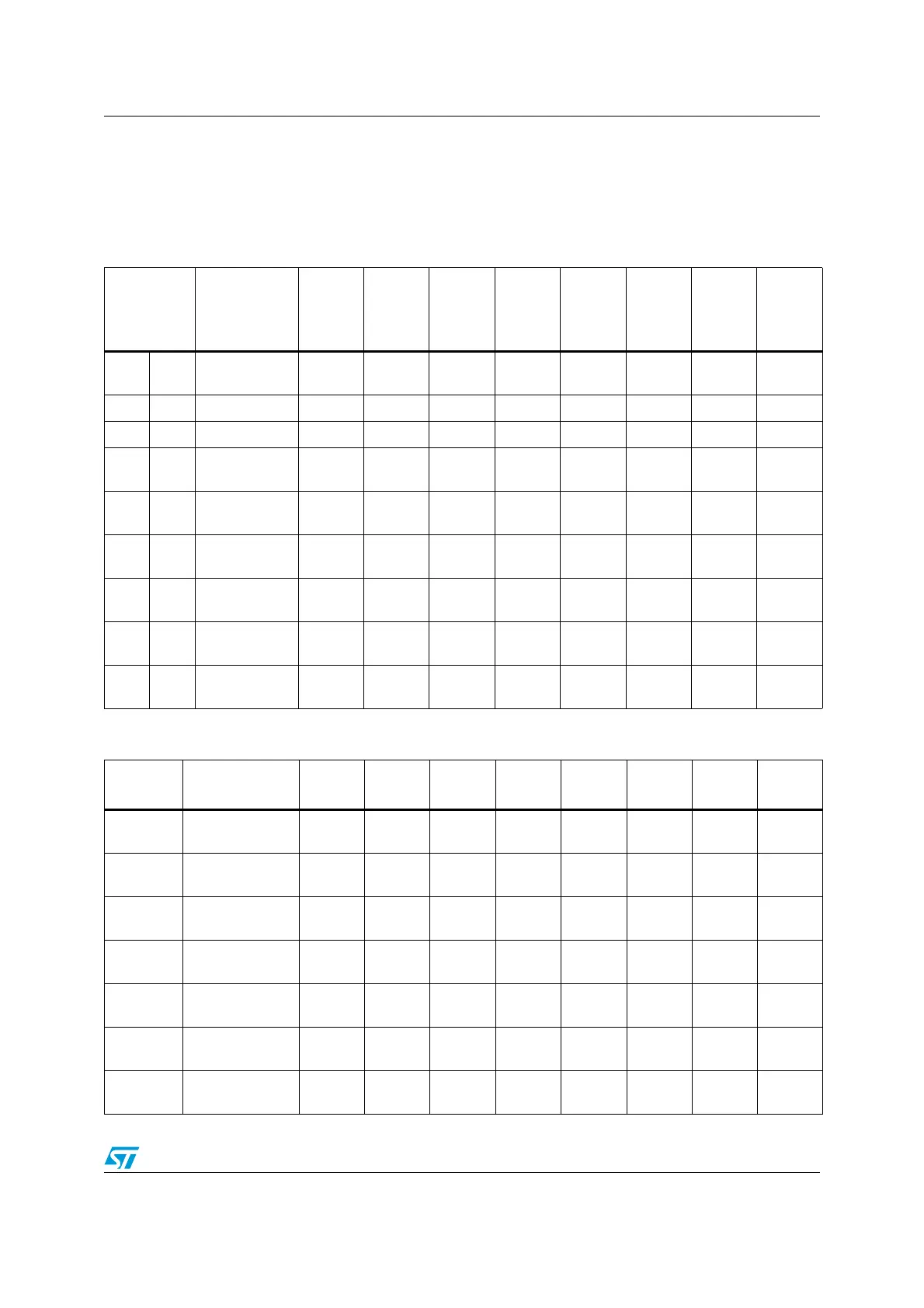

19.6.10 TIM4/TIM6 register map and reset values

In some STM8S and STM8A devices, TIM4 register locations at offset 0x01 and 0x02 are

reserved. In this case the TIM4_IER and subsequent registers in the TIM4 block are offset

by 2 more bytes. Refer to the datasheet for the product-specific register map.

Table 43. TIM4 register map

Address

offset

(product

dependent)

Register

name

76543210

0x00 0x00

TIM4_CR1

Reset value

ARPE

0

-

0

-

0

-

0

OPM

0

URS

0

UDIS

0

CEN

0

- 0x01 Reserved

- 0x02 Reserved

0x01 0x03

TIM4_IER

Reset value

-

0

-

0

-

0

-

0

-

0

-

0

-

0

UIE

0

0x02 0x04

TIM4_SR

Reset value

-

0

-

0

-

0

-

0

-

0

-

0

-

0

UIF

0

0x03 0x05

TIM4_EGR

Reset value

-

0

-

0

-

0

-

0

-

0

-

0

-

0

UG

0

0x04 0x06

TIM4_CNTR

Reset value

CNT7

0

CNT6

0

CNT5

0

CNT4

0

CNT3

0

CNT2

0

CNT1

0

CNT0

0

0x05 0x07

TIM4_PSCR

Reset value

-

0

-

0

-

0

-

0

-

0

PSC2

0

PSC1

0

PSC0

0

0x06 0x08

TIM4_ARR

Reset value

ARR7

1

ARR6

1

ARR5

1

ARR4

1

ARR3

1

ARR2

1

ARR1

1

ARR0

1

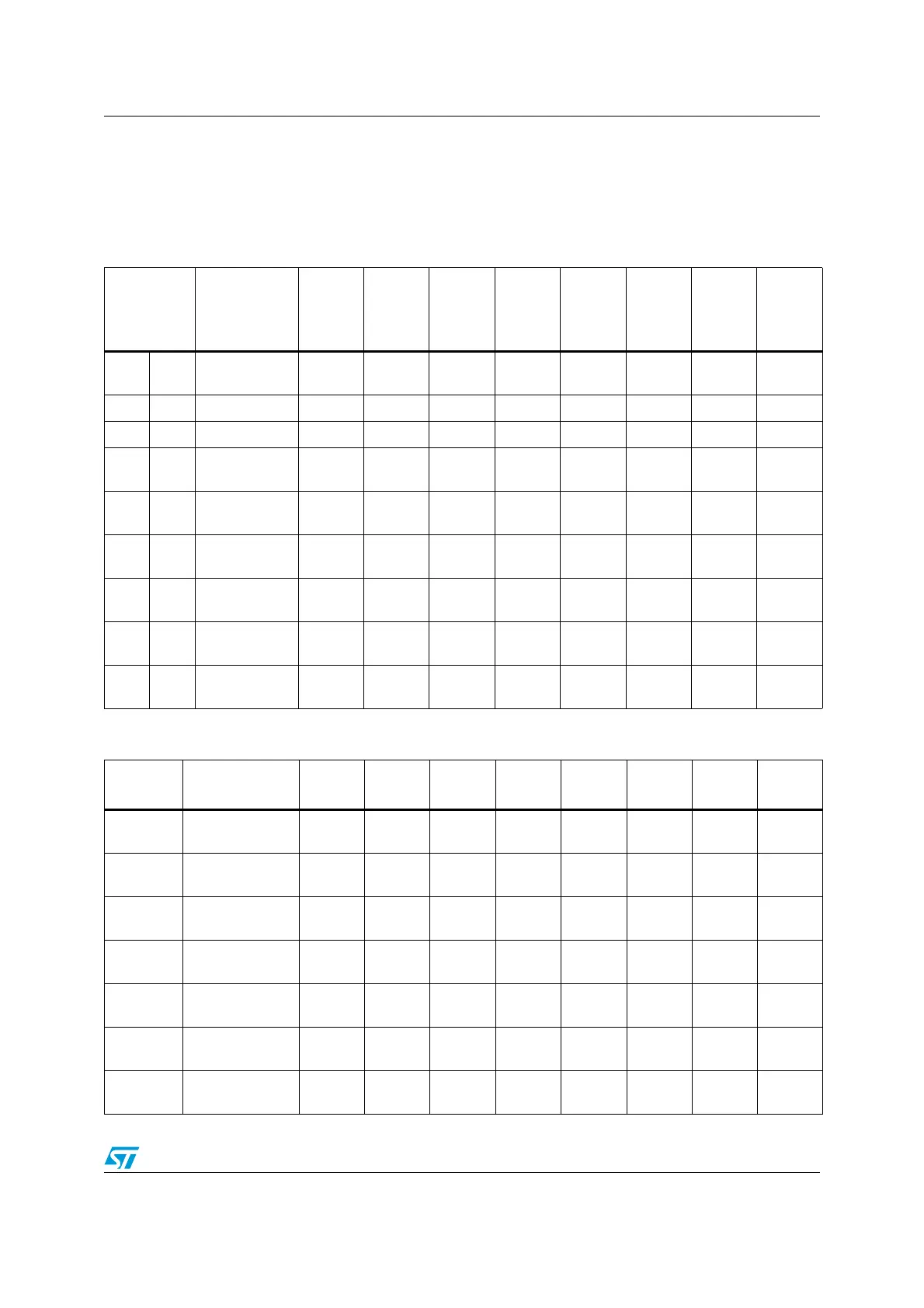

Table 44. TIM6 register map

Address

offset

Register name76543210

0x00

TIM6_CR1

Reset value

ARPE

0

-

0

-

0

-

0

OPM

0

URS

0

UDIS

0

CEN

0

0x01

TIM6_CR2

Reset value

-

0

MMS2

0

MMS1

0

MMS0

0

-

0

-

0

-

0

-

0

0x02

TIM6_SMCR

Reset value

MSM

0

TS2

0

TS1

0

TS0

0

-

0

SMS2

0

SMS1

0

SMS0

0

0x03

TIM6_IER

Reset value

-

0

TIE

0

-

0

-

0

-

0

-

0

-

0

UIE

0

0x04

TIM6_SR1

Reset value

-

0

TIF

0

-

0

-

0

-

0

-

0

-

0

UIF

0

0x05

TIM6_EGR

Reset value

-

0

TG

0

-

0

-

0

-

0

-

0

-

0

UG

0

0x06

TIM6_CNTR

Reset value

CNT7

0

CNT6

0

CNT5

0

CNT4

0

CNT3

0

CNT2

0

CNT1

0

CNT0

0

Loading...

Loading...