RM0016 Analog/digital converter (ADC)

Doc ID 14587 Rev 8 429/449

24.11.5 ADC configuration register 2 (ADC_CR2)

Address offset: 0x22

Reset value: 0x00

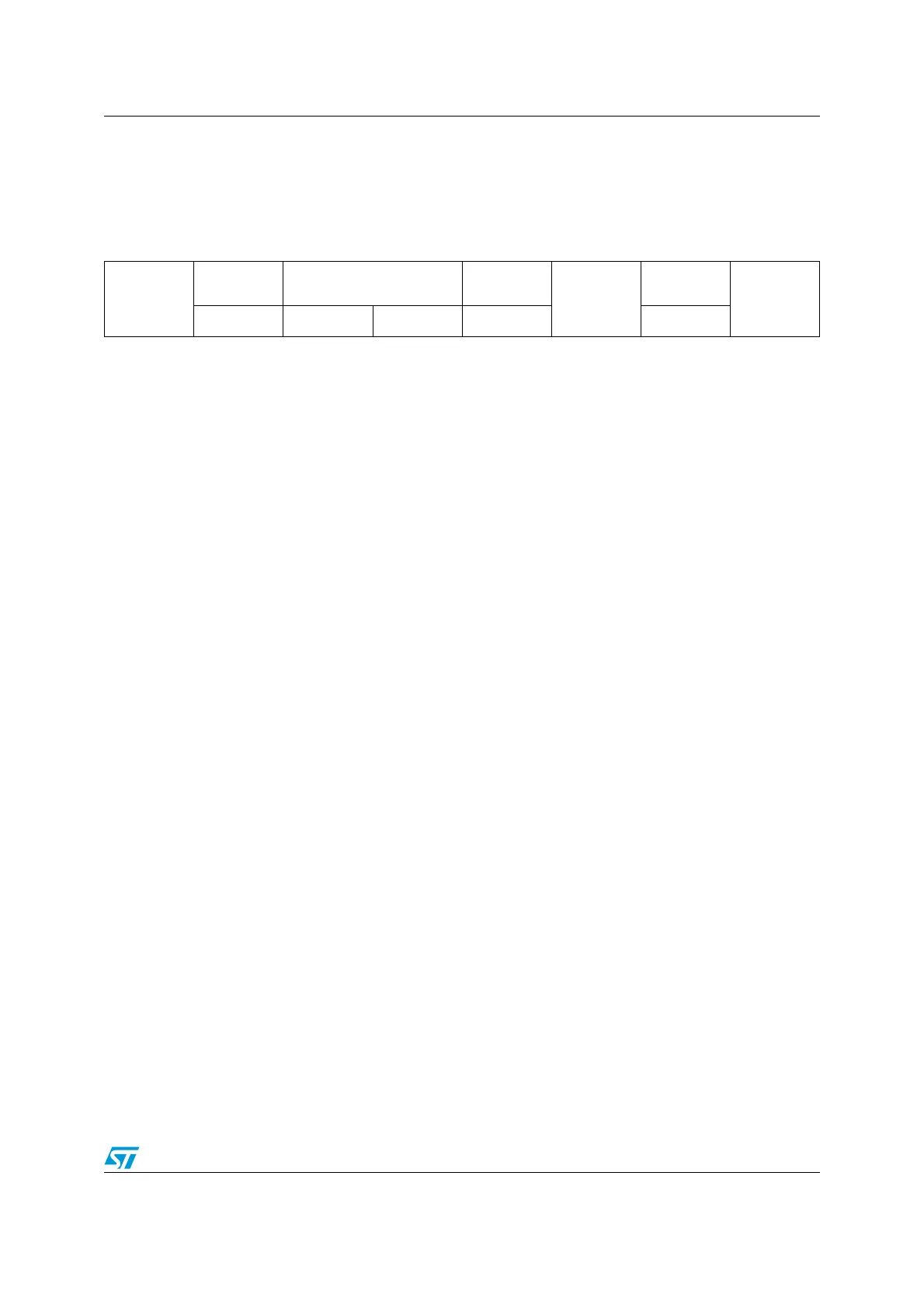

76543210

Reserved

EXTTRIG EXTSEL[1:0] ALIGN

Reserved

SCAN

Reserved

rw rw rw rw rw

Bit 7 Reserved, must be kept cleared.

Bit 6 EXTTRIG: External trigger enable

This bit is set and cleared by software. It is used to enable an external trigger to

trigger a conversion.

0: Conversion on external event disabled

1: Conversion on external event enabled

Note: To avoid a spurious trigger event, use the BSET instruction to set

EXTTRIG without changing other bits in the register.

Bits 5:4 EXTSEL[1:0]: External event selection

The two bits are written by software. They select one of four types of event used

to trigger the start of ADC conversion.

00: Internal TIM1 TRGO event

01: External interrupt on ADC_ETR pin

10: Reserved

11: Reserved

Bit 3 ALIGN: Data alignment

This bit is set and cleared by software.

0: Left alignment (the eight MSB bits are written in the ADC_DRH register then

the remaining LSB bits are written in the ADC_DRL register). The reading order

should be MSB first and then LSB.

1: Right alignment (eight LSB bits are written in the ADC_DRL register then the

remaining MSB bits are written in the ADC_DH register). The reading order

should be LSB first and then MSB.

Note: The ALIGN bit influences the ADC_DRH/ADC_DRL register reading

order and not the reading order of the buffer registers.

Bit 2 Reserved, must be kept cleared.

Bit 1 SCAN: Scan mode enable

This bit is set and cleared by software.

0: Scan mode disabled

1: Scan mode enabled

Note: This bit is not available for ADC2

Bit 0 Reserved, must be kept cleared.

Loading...

Loading...