Interrupt controller (ITC) RM0016

68/449 Doc ID 14587 Rev 8

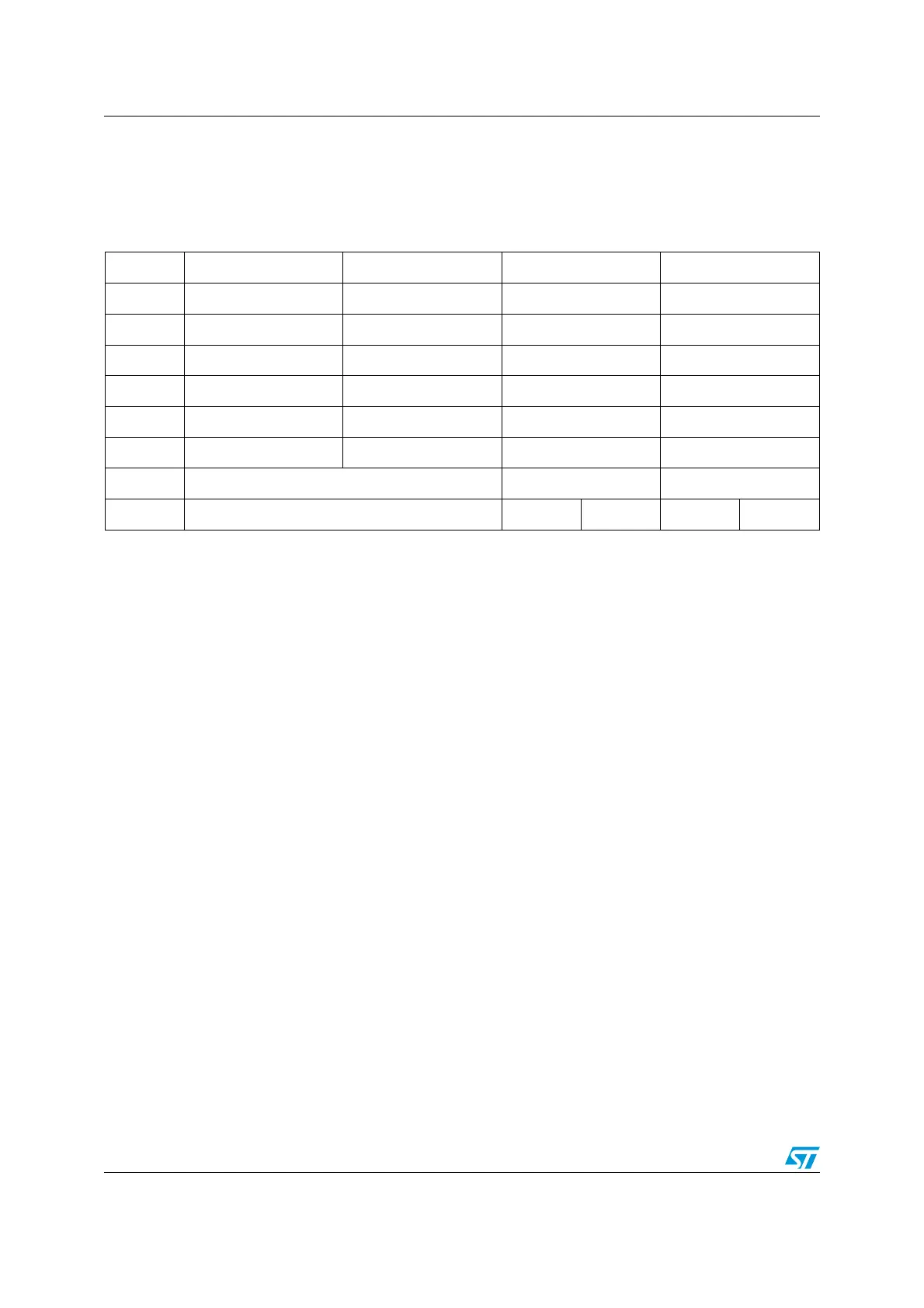

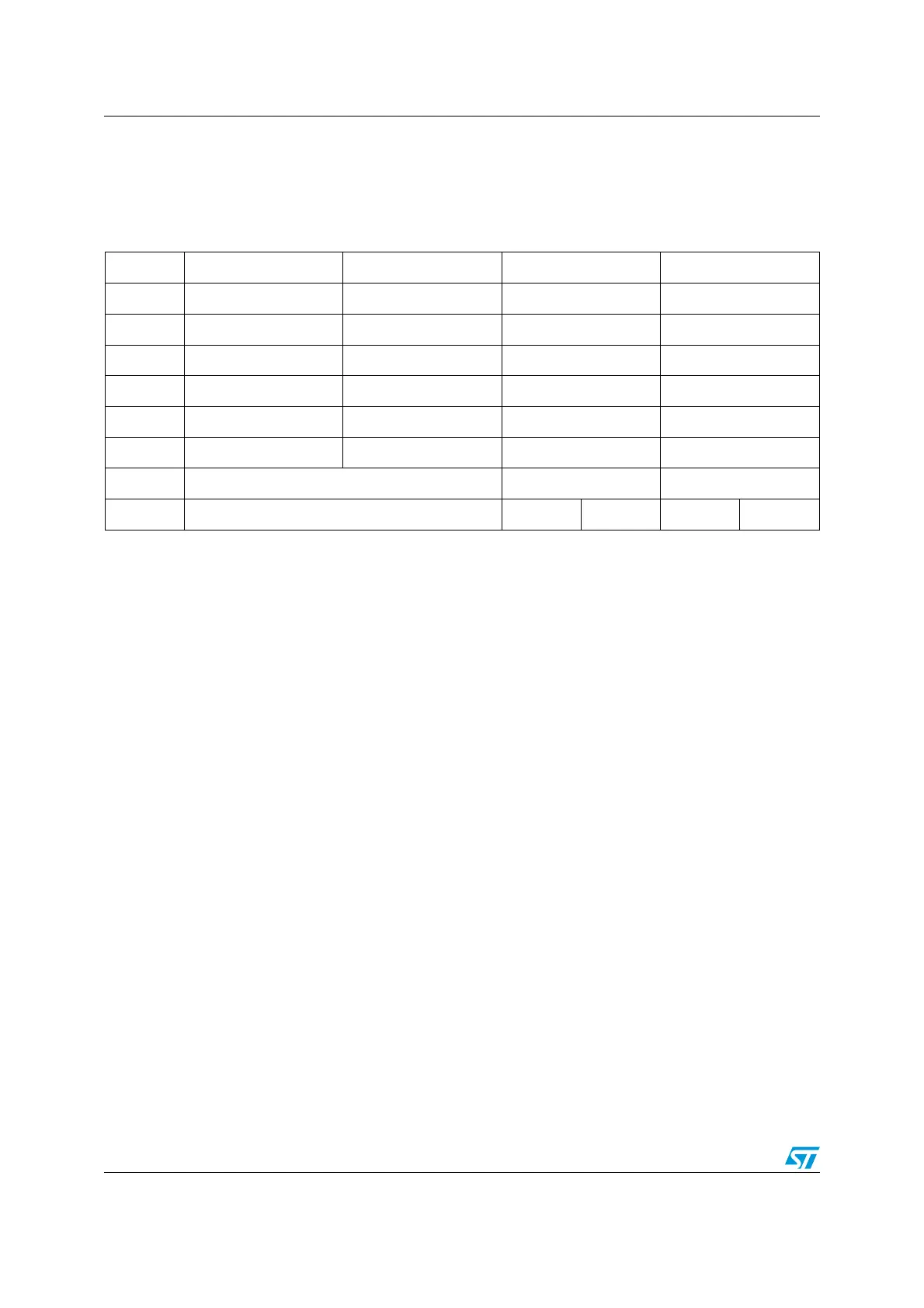

6.9.2 Software priority register x (ITC_SPRx)

Address offset: 0x00 to 0x07

Reset value: 0xFF

76543210

ITC_SPR1 VECT3SPR[1:0] VECT2SPR[1:0] VECT1SPR[1:0] VECT0SPR[1:0]

ITC_SPR2 VECT7SPR[1:0] VECT6SPR[1:0] VECT5SPR[1:0] VECT4SPR[1:0]

ITC_SPR3 VECT11SPR[1:0] VECT10SPR[1:0] VECT9SPR[1:0] VECT8SPR[1:0]

ITC_SPR4 VECT15SPR[1:0] VECT14SPR[1:0] VECT13SPR[1:0] VECT12SPR[1:0]

ITC_SPR5 VECT19SPR[1:0] VECT18SPR[1:0] VECT17SPR[1:0] VECT16SPR[1:0]

ITC_SPR6 VECT23SPR[1:0] VECT22SPR[1:0] VECT21SPR[1:0] VECT20SPR[1:0]

ITC_SPR7 VECT27SPR[1:0] VECT26SPR[1:0] VECT25SPR[1:0] VECT24SPR[1:0]

ITC_SPR8 Reserved VECT29SPR[1:0] VECT28SPR[1:0]

rw rw rw rw rw

Bits 7:0 VECTxSPR[1:0]: Vector x software priority bits

These eight read/write registers (ITC_SPR1 to ITC_SPR8) are written by software to define

the software priority of each interrupt vector.

The list of vectors is given in Table 10: Vector address map versus software priority bits.

Refer to Section 6.9.1: CPU condition code register interrupt bits (CCR) for the values to be

programmed for each priority.

ITC_SPR1 bits 1:0 are forced to 1 by hardware (TLI)

ITC_SPR8 bits 7:4 are forced to 1 by hardware.

Note: It is forbidden to write 10 (priority level 0). If 10 is written, the previous value is kept

and the interrupt priority remains unchanged.

Loading...

Loading...