RM0016 Inter-integrated circuit (I

2

C) interface

Doc ID 14587 Rev 8 283/449

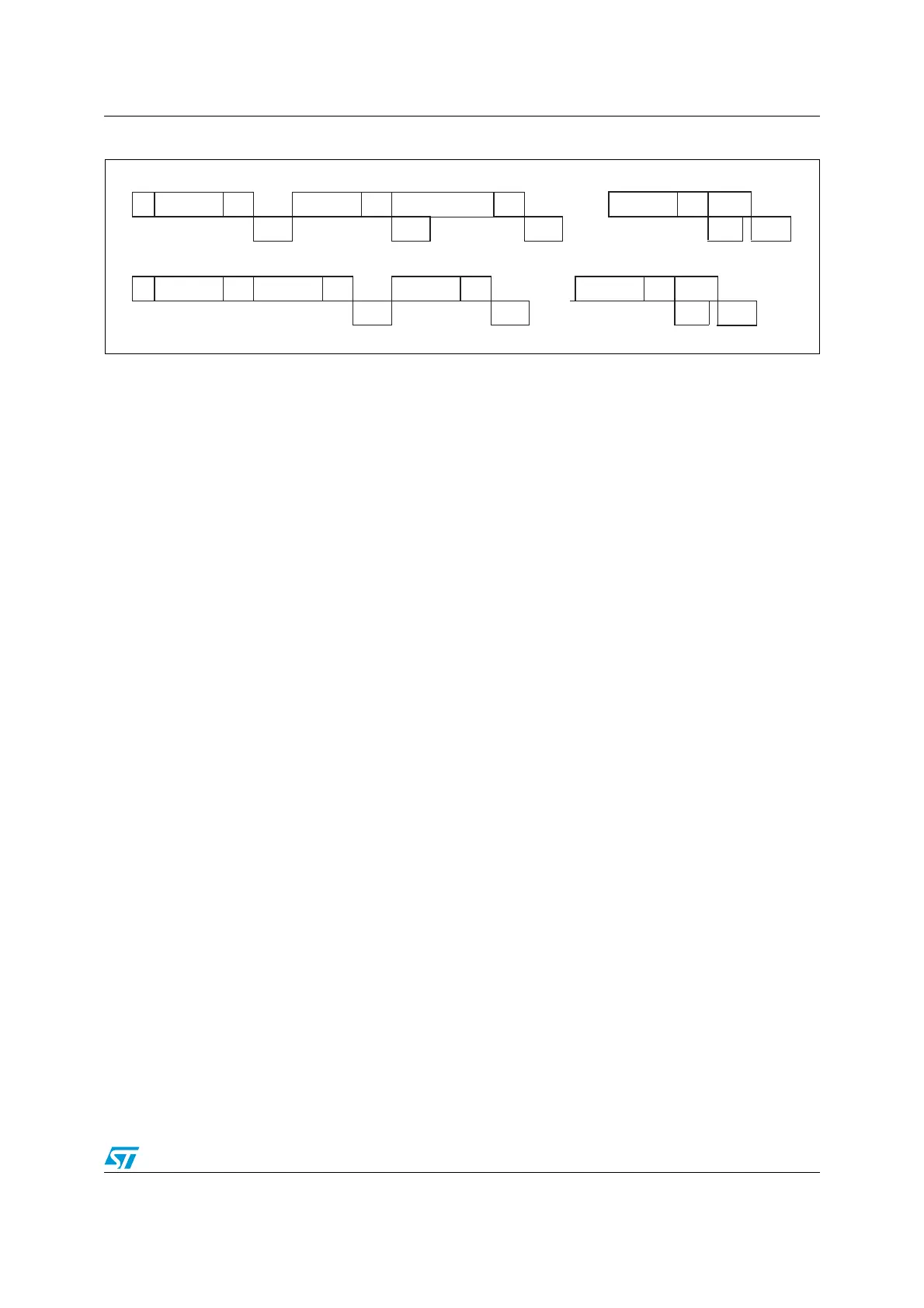

Figure 103. Transfer sequence diagram for slave receiver

1. Legend:

S= Start, S

r

= Repeated Start, P= Stop, A= Acknowledge, NA= Non-acknowledge, EVx= Event (with interrupt if

ITEVTEN=1)

EV1: ADDR =1, cleared by reading SR1 register followed by reading SR3.

EV2: RXNE=1, cleared by reading DR register.

EV4: STOPF=1, cleared by reading SR1 register followed by writing CR2 register

2. EV1 event stretches SCL low until the end of the corresponding software sequence.

3. EV2 software sequence must be performed before the end of the current byte transfer.

4. After checking the SR1 register content, the user should perform the complete clearing sequence for each flag found set.

Thus, for the ADDR and STOPF flags, the following sequence is recommended inside the I2C interrupt routine:

READ SR1

if (ADDR == 1) {READ SR1; READ SR3}

if (STOPF == 1) {READ SR1; WRITE CR2}

The purpose is to make sure that both ADDR and STOPF flags are cleared if both are found set.

5. See also: Note 8 on page 300.

Closing slave communication

After the last data byte is transferred, a Stop condition is generated by the master. The

interface detects this condition and sets the STOPF bit and generates an interrupt if the

ITEVTEN bit is set.

STOPF is cleared by a read of the SR1 register followed by a write to the CR2 register (see

Figure 104).

21.4.2 I

2

C master mode

In Master mode, the I

2

C interface initiates a data transfer and generates the clock signal. A

serial data transfer always begins with a Start condition and ends with a Stop condition.

Master mode is selected as soon as the Start condition is generated on the bus with a

START bit.

The following is the required sequence in master mode.

● Program the peripheral input clock in I2C_FREQR Register in order to generate correct

timings.

● Configure the clock control registers

● Configure the rise time register

● Program the I2C_CR1 register to enable the peripheral

● Set the START bit in the I2C_CR2 register to generate a Start condition

The peripheral input clock frequency must be at least:

● 1 MHz in Standard mode

● 4 MHz in Fast mode

7-bit slave receiver

10-bit slave receiver

S Address AData1AData2A

.....

DataNA

P

EV1 EV2 EV2 EV2 EV4

S Header A Address AData1A

.....

DataNA P

EV1 EV2 EV2

EV4

ai18208

Loading...

Loading...