RM0016 Window watchdog (WWDG)

Doc ID 14587 Rev 8 127/449

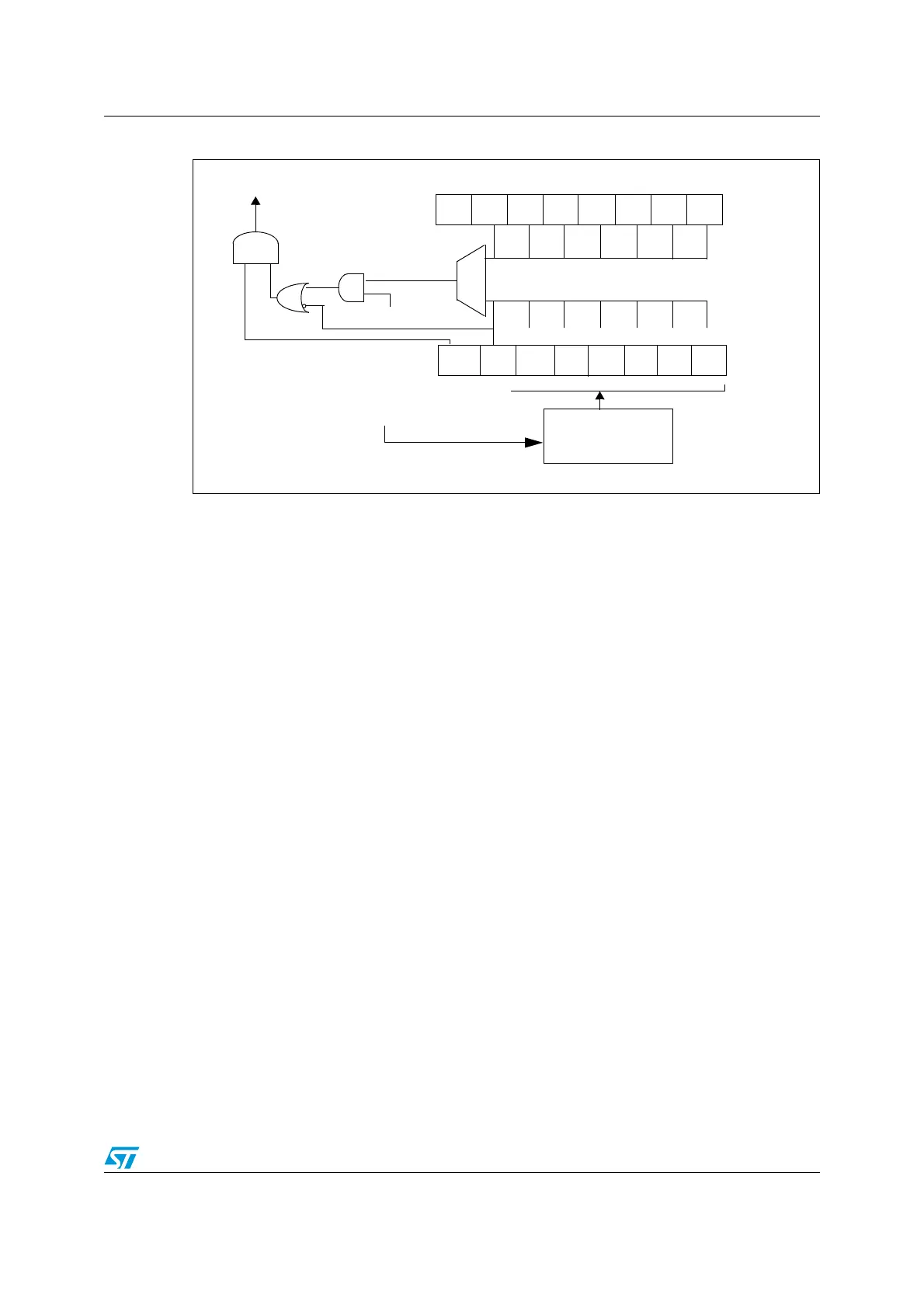

Figure 28. Watchdog block diagram

The application program must write in the WWDG_CR register at regular intervals during

normal operation to prevent an MCU reset. This operation must occur only when the counter

value is lower than the window register value. The value to be stored in the WWDG_CR

register must be between 0xFF and 0xC0 (see Figure 29):

● Enabling the watchdog:

When software watchdog is selected (by option byte), the watchdog is disabled after a

reset. It is enabled by setting the WDGA bit in the WWDG_CR register, then it cannot

be disabled again except by a reset.

When hardware watchdog is selected (by option byte), the watchdog is always active

and the WDGA bit is not used.

● Controlling the downcounter:

This downcounter is free-running: It counts down even if the watchdog is disabled.

When the watchdog is enabled, the T6 bit must be set to prevent generating an

immediate reset.

The T[5:0] bits contain the number of increments which represents the time delay

before the watchdog produces a reset (see Figure 29: Approximate timeout duration).

The timing varies between a minimum and a maximum value due to the unknown

status of the prescaler when writing to the WWDG_CR register (see Figure 30).

The window register (WWDG_WR) contains the high limit of the window: To prevent a

reset, the downcounter must be reloaded when its value is lower than the window

register value and greater than 0x3F. Figure 30 describes the window watchdog

process.

Note: The T6 bit can be used to generate a software reset (the WDGA bit is set and the T6 bit is

cleared).

● Watchdog reset on halt option

If the watchdog is activated and the watchdog reset on halt option is selected, then the

HALT instruction will generate a reset.

RESET

WDGA

6-BIT DOWNCOUNTER (CNT)

T6

WATCHDOG CONTROL REGISTER (wWDG_CR)

T1

T2

T3

T4

T5

-

W6

W0

WATCHDOG WINDOW REGISTER (WWDG_WR)

W1

W2

W3

W4

W5

comparator

T6:0 > W6:0

CMP

= 1 when

Write WWDG_CR

WDG PRESCALER

DIV 12288

f

CPU

T0

(from clock)

Loading...

Loading...