16-bit advanced control timer (TIM1) RM0016

208/449 Doc ID 14587 Rev 8

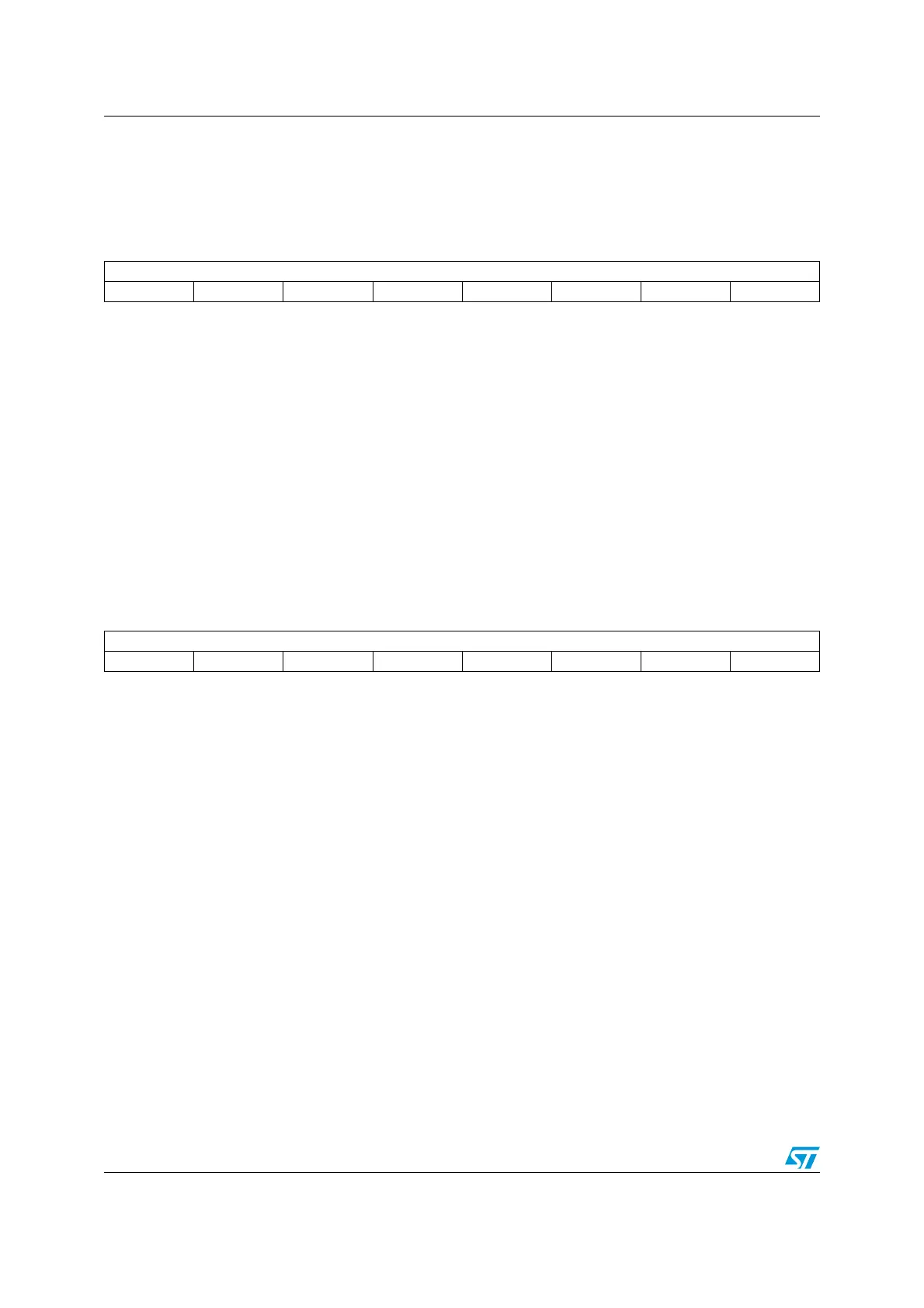

17.7.24 Capture/compare register 2 high (TIM1_CCR2H)

Address offset: 0x17

Reset value: 0x00

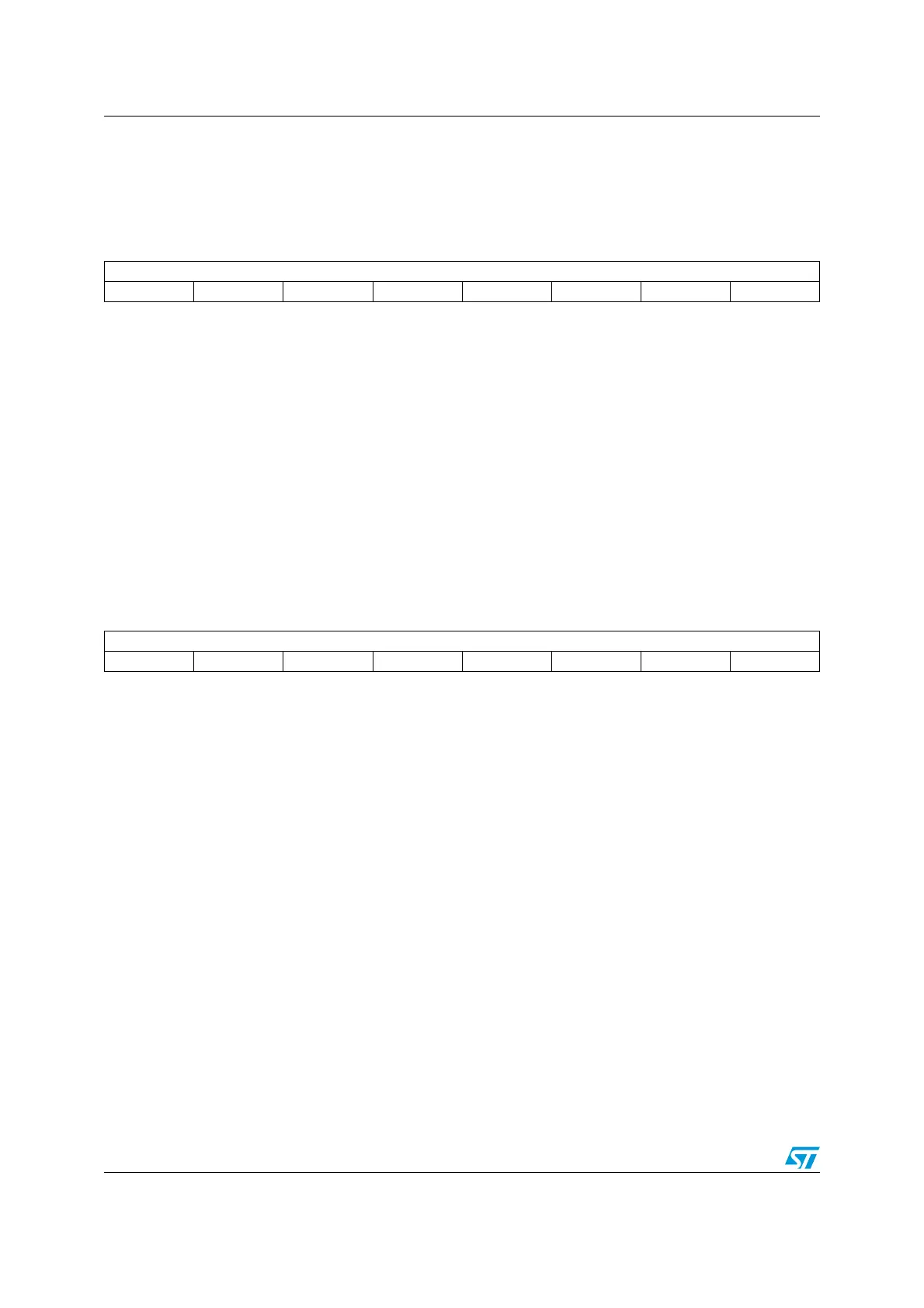

17.7.25 Capture/compare register 2 low (TIM1_CCR2L)

Address offset: 0x18

Reset value: 0x00

76543210

CCR2[15:8]

rw rw rw rw rw rw rw rw

Bits 7:0 CCR2[15:8]: Capture/compare 2 value (MSB)

If the CC2 channel is configured as output (CC2S bits in TIM1_CCMR2 register):

The value of CCR2 is loaded permanently into the actual capture/compare 2 register if the preload

feature is not enabled (OC2PE bit in TIM1_CCMR2). Otherwise, the preload value is copied in the

active capture/compare 2 register when a UEV occurs.The active capture/compare register contains

the value which is compared to the counter register, TIM1_CNT, and signalled on the OC2 output.

If the CC2 channel is configured as input (CC2S bits in TIM1_CCMR2 register):

The value of CCR2 is the counter value transferred by the last input capture 2 event (IC2). In this

case, these bits are read only.

76543210

CCR2[7:0]

rw rw rw rw rw rw rw rw

Bits 7:0 CCR2[7:0]: Capture/compare value (LSB)

Loading...

Loading...