Universal asynchronous receiver transmitter (UART) RM0016

346/449 Doc ID 14587 Rev 8

22.5 UART low power modes

22.6 UART interrupts

Note: 1 The UART interrupt events are connected to two interrupt vectors (see Figure 138).

a) Transmission Complete or Transmit Data Register empty interrupt.

b) Idle Line detection, Overrun error, Receive Data register full, Parity error interrupt,

and Noise Flag.

2 These events generate an interrupt if the corresponding Enable Control Bit is set and the

interrupt mask in the CC register is reset (RIM instruction).

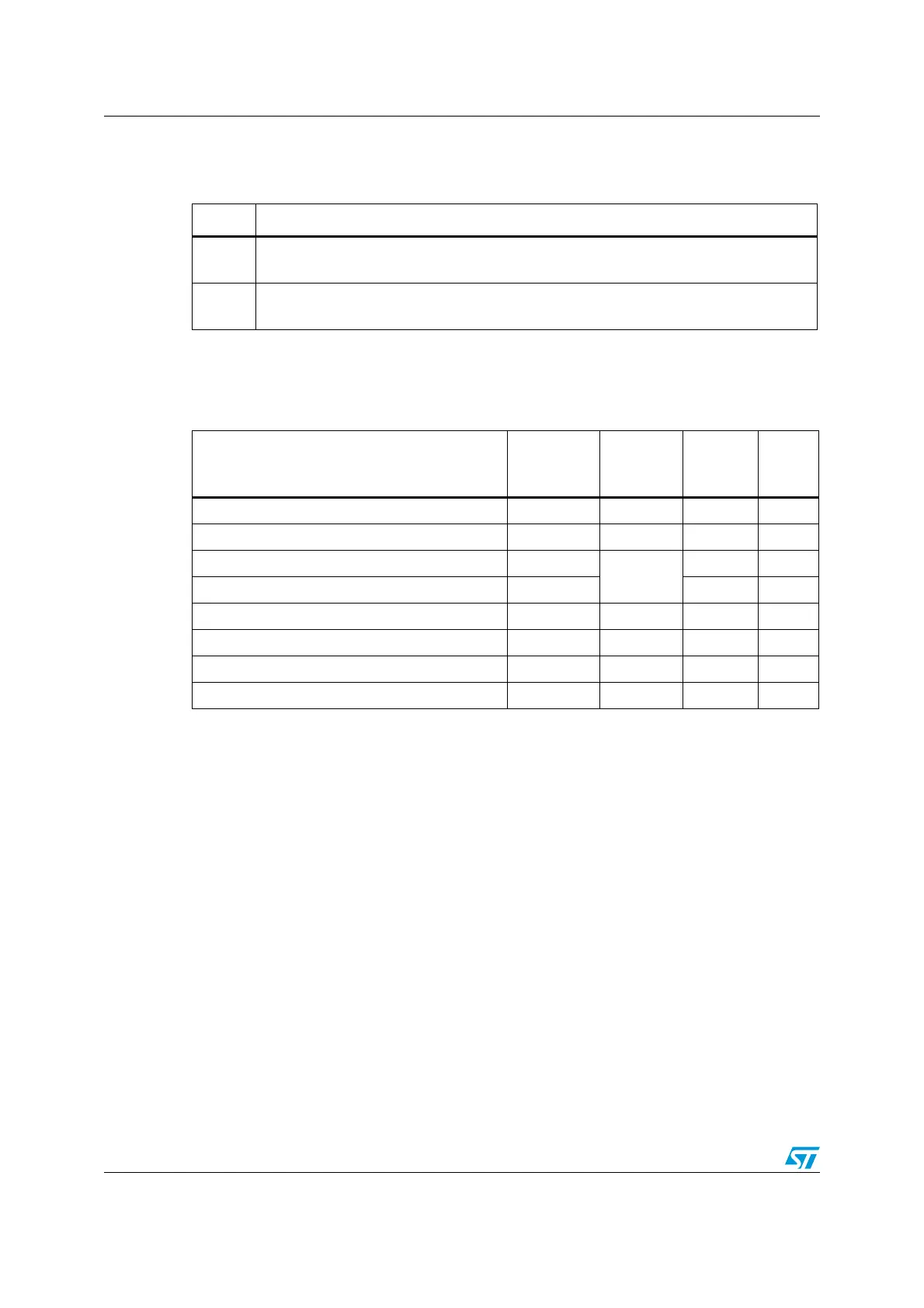

Table 59. UART interface behavior in low power modes

Mode Description

Wait

No effect on UART.

UART interrupts cause the device to exit from Wait mode.

Halt

UART registers are frozen.

In Halt mode, the UART stops transmitting/receiving until Halt mode is exited.

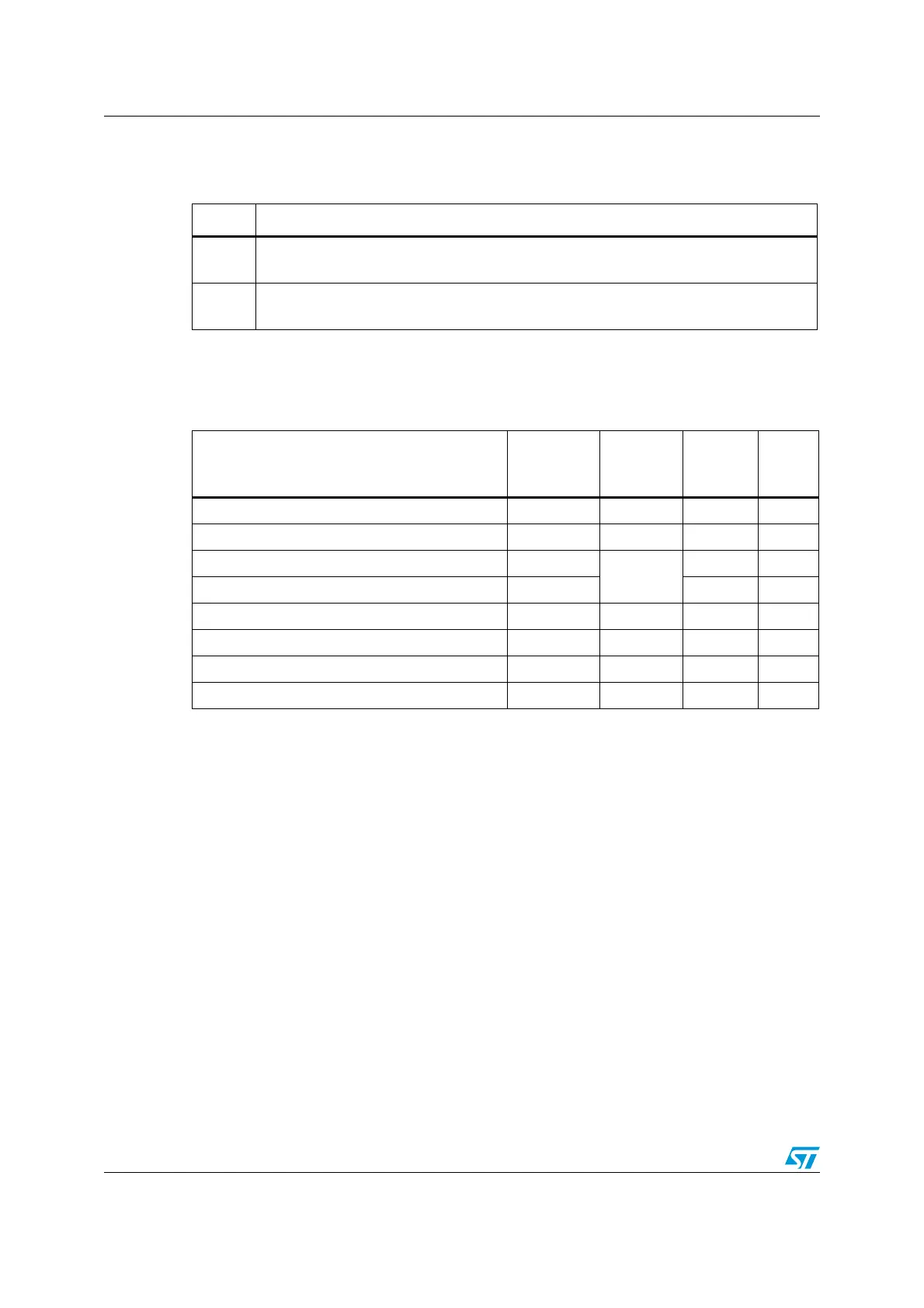

Table 60. UART interrupt requests

Interrupt event

Event

flag

Enable

control

bit

Exit

from

Wait

Exit

from

Halt

Transmit data register empty TXE TIEN Yes No

Transmission complete TC TCIEN Yes No

Received data ready to be read RXNE

RIEN

Ye s N o

Overrun error detected / LIN header error OR/LHE Yes No

Idle line detected IDLE ILIEN Yes No

Parity error PE PIEN Yes No

Break flag LBDF LBDIEN Yes No

Header Flag LHDF LHDIEN Yes No

Loading...

Loading...