Analog/digital converter (ADC) RM0016

412/449 Doc ID 14587 Rev 8

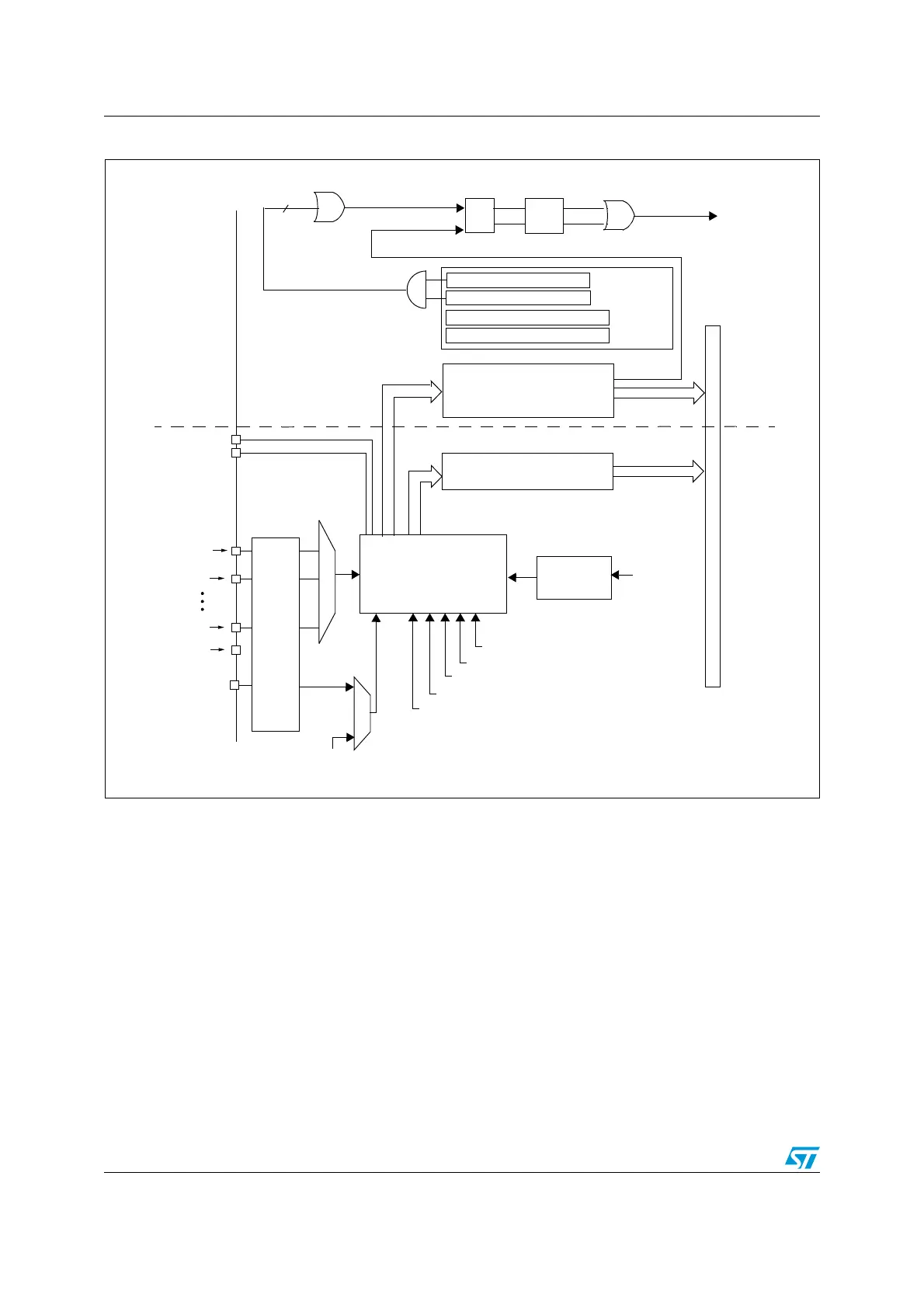

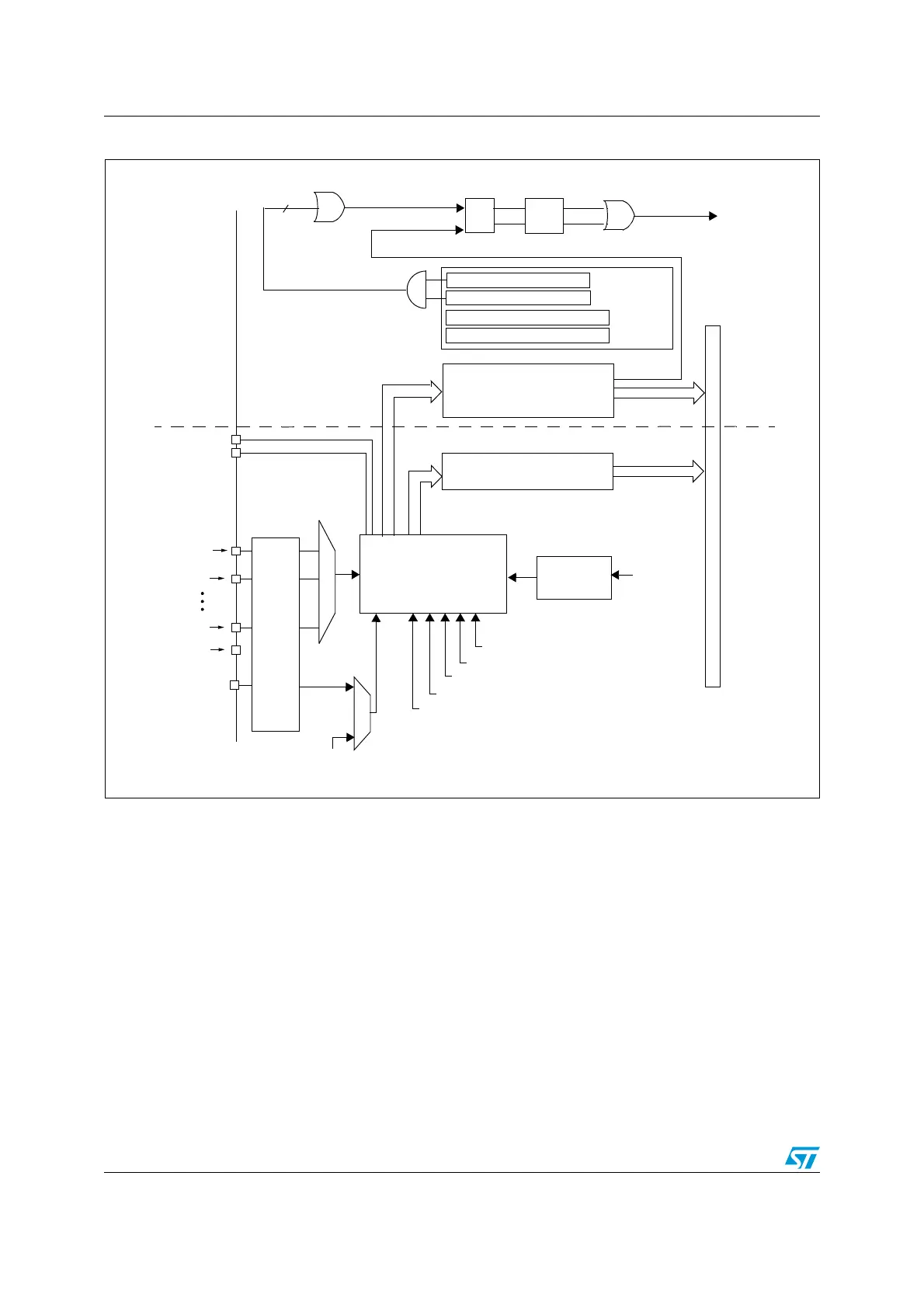

Figure 158. ADC1 block diagram

1. Refer to the product datasheet for AIN12 availability.

AIN0

AIN1

ANALOG TO DIGITAL

CONVERTER

AIN9

ANALOG

MUX

Prescaler

f

ADC

GPIO

Ports

Address/data bus

DATA REGISTER

(1 x 10-bits)

V

DDA

V

SSA

/2, /3, /4, ..../18

f

MASTER

ADC_ETR

Internal TRGO trigger from TIM1

End of Conversion

ADC Interrupt to ITC

ANALOG

WATCHDOG

DATA BUFFER

(10 x 10 bits) or (8 x 10 bits)

Low Threshold (10-bits)

AWEN Enable bits (10

channels

)

AWS status bits (10 channels)

High Threshold (10-bits)

Flags Masks

EOC

AWD

EOCIE

AWDIE

Analog Watchdog Event

10

SPSEL Channel select

CONT Single/continuous mode

ADON Start conversion (software)

SCAN Scan mode

DBUF Buffered mode

AIN12

Loading...

Loading...