RM0016 Serial peripheral interface (SPI)

Doc ID 14587 Rev 8 271/449

Restrictions in receive-only modes

The wake-up functionality is not guaranteed in receive-only modes (BDM = 0 and

RXONLY = 1 or BDM = 1 and BDOE = 0) since the time needed to restore the system clock

can be greater than the data reception time. A loss of data in reception would then be

induced and the slave device can not indicate to the master which data has been properly

received.

20.3.11 SPI interrupts

20.4 SPI registers

20.4.1 SPI control register 1 (SPI_CR1)

Address offset: 0x00

Reset value: 0x00

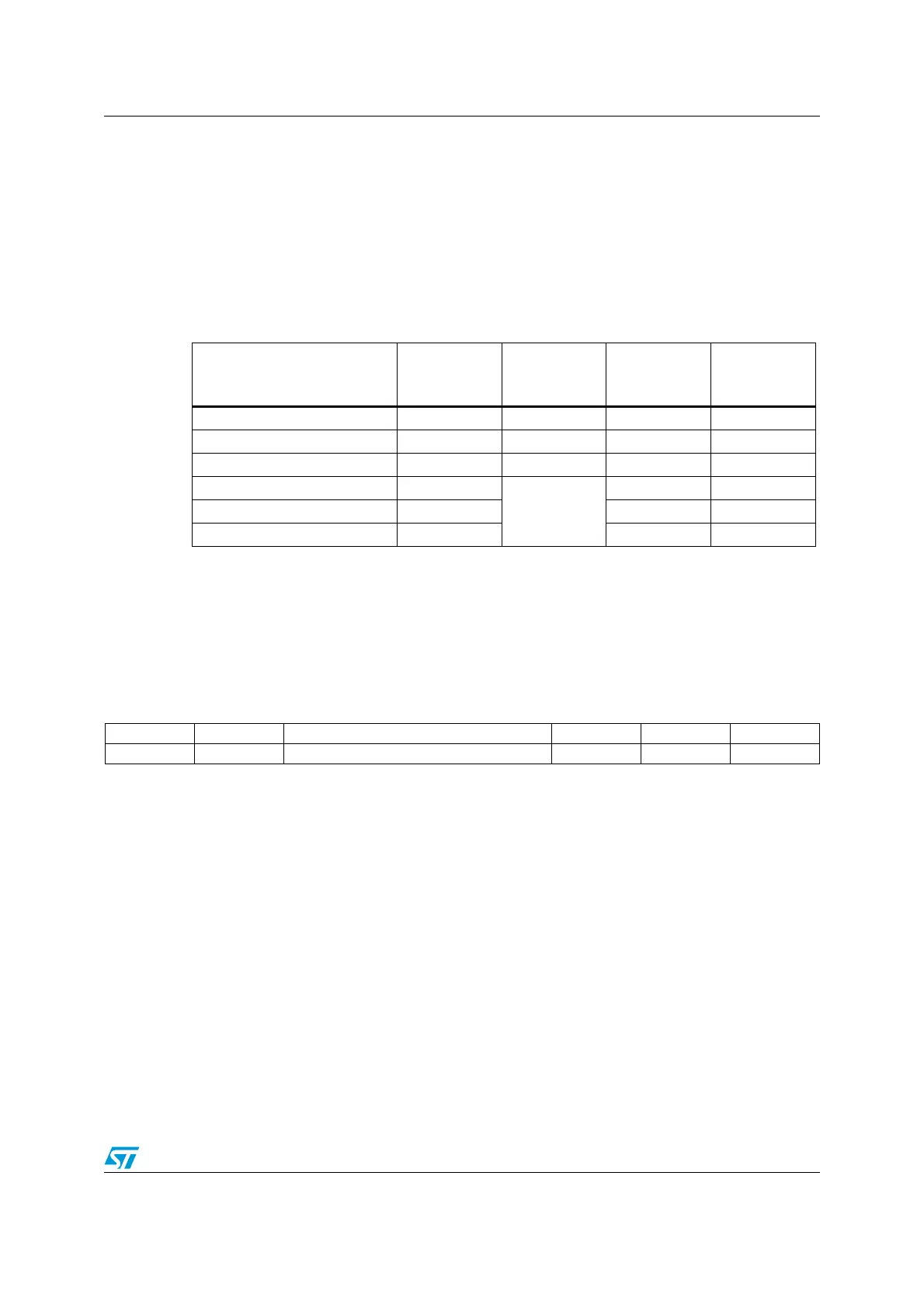

Table 46. SPI interrupt requests

Interrupt event

Event

flag

Enable

control

bit

Exit

from

Wait

Exit

from

Halt

Transmit buffer empty flag TXE TXIE Yes No

Receive buffer not empty flag RXNE RXIE Yes No

Wakeup event flag WKUP WKIE Yes Yes

Master mode fault event MODF

ERRIE

Yes No

Overrun error OVR Yes No

CRC error flag CRCERR Yes No

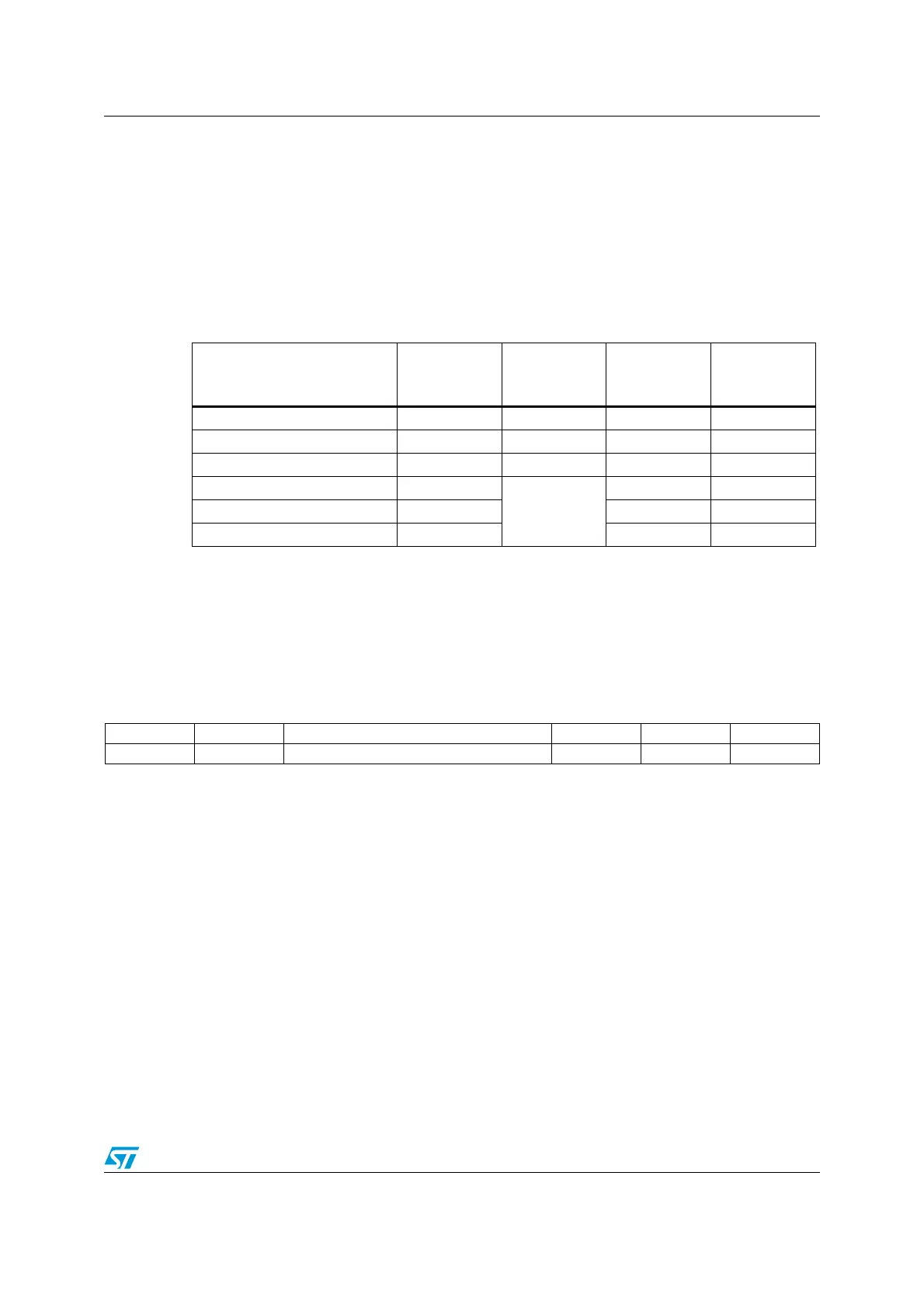

76543210

LSBFIRST SPE BR [2:0] MSTR CPOL CPHA

rw rw rw rw rw rw

Bit 7 LSBFIRST: Frame format

(1)

0: MSB is transmitted first

1: LSB is transmitted first

Bit 6 SPE: SPI enable

(2)

0: Peripheral disabled

1: Peripheral enabled

Bits 5:3 BR[2:0]: Baud rate control

000: f

MASTER

/2 100: f

MASTER

/32

001: f

MASTER

/4 101: f

MASTER

/64

010: f

MASTER

/8 110: f

MASTER

/128

011: f

MASTER

/16 111: f

MASTER

/256

Note: These bits should not be changed when the communication is ongoing.

Bit 2 MSTR: Master selection

(1)

0: Slave configuration

1: Master configuration

Loading...

Loading...