RM0016 16-bit advanced control timer (TIM1)

Doc ID 14587 Rev 8 195/449

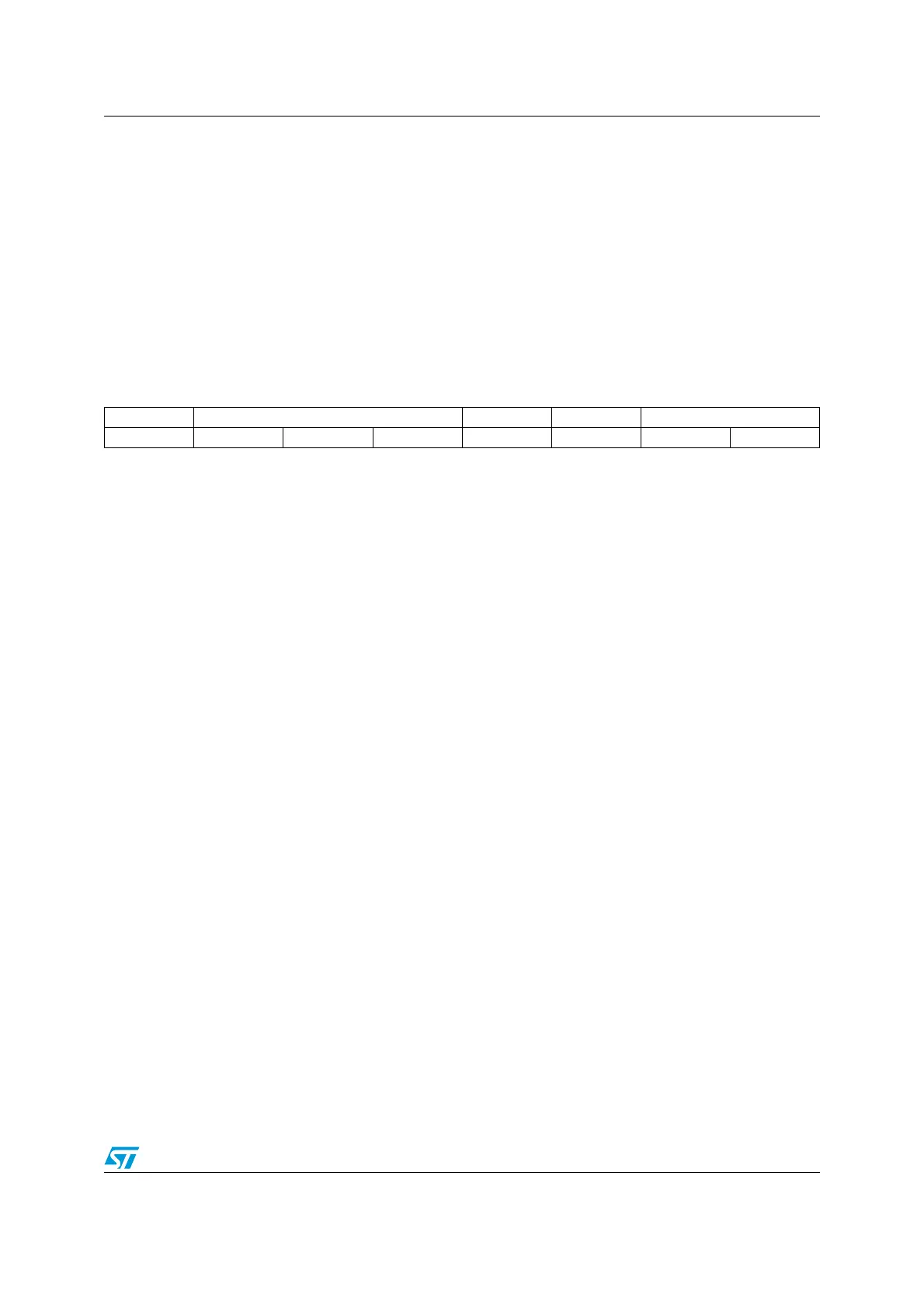

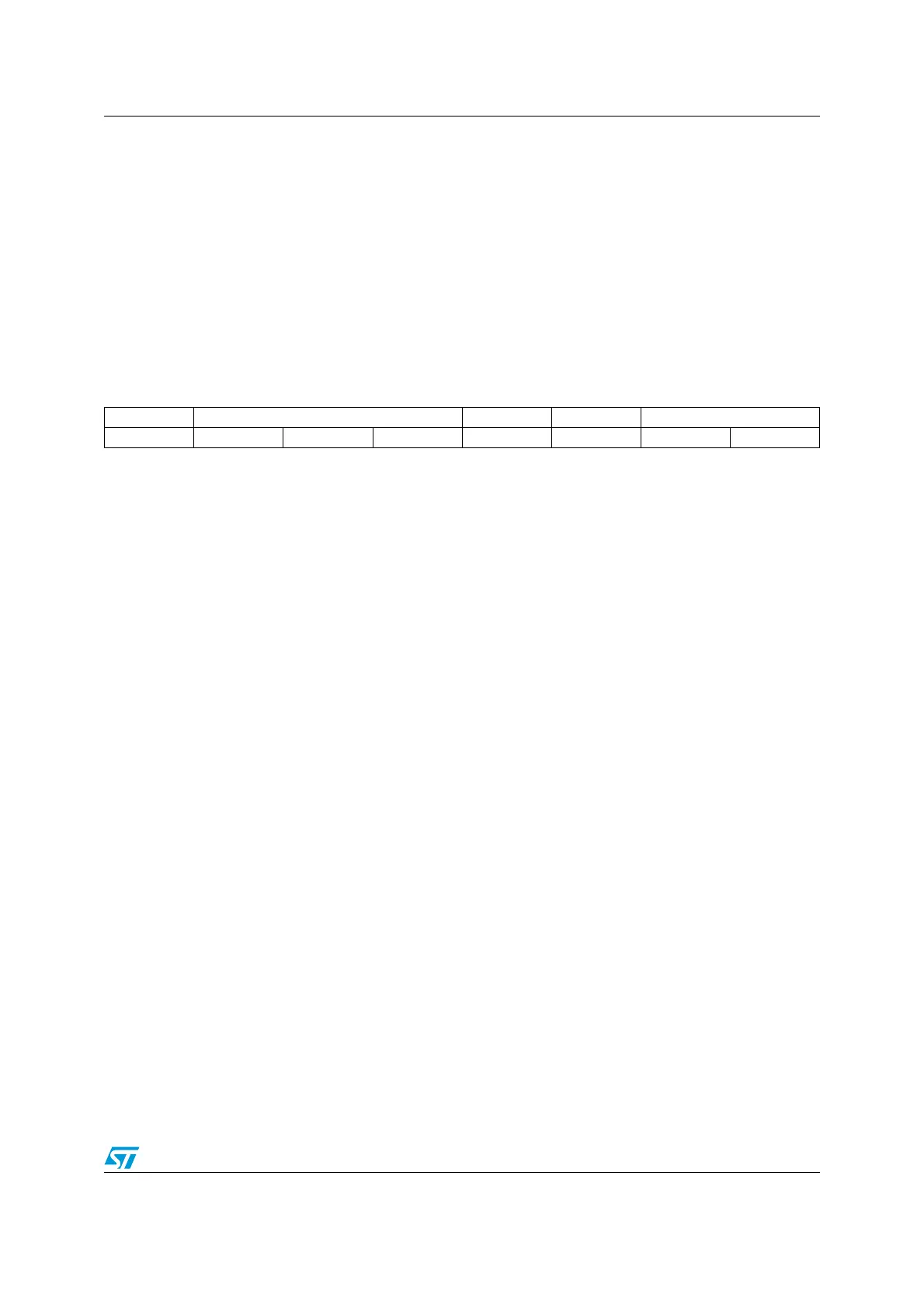

17.7.9 Capture/compare mode register 1 (TIM1_CCMR1)

Address offset: 0x08

Reset value: 0x00

This channel can be used in input (capture mode) or in output (compare mode). The

direction of the channel is defined by configuring the CC1S bits. All the other bits of this

register have a different function in input and output mode. For a given bit, OCii describes its

function when the channel is configured in output, ICii describes its function when the

channel is configured in input. Therefore, be aware that the same bit can have a different

meaning for the input and output stage.

Channel configured in output

76543210

OC1CE OC1M[2:0] OC1PE OC1FE CC1S[1:0]

rw rw rw rw rw rw rw rw

Bit 7 OC1CE: Output compare 1 clear enable

This bit is used to enable the clearing of the channel 1 output compare signal (OC1REF) by an

external event on the TIM1_ETR pin (see Section 17.5.9 on page 181).

0: OC1REF is not affected by the ETRF input signal (derived from the TIM1_ETR pin)

1: OC1REF is cleared as soon as a high level is detected on ETRF input signal (derived from the

TIM1_ETR pin).

Bits 6:4 OC1M: Output compare 1 mode

These bits define the behavior of the output reference signal, OC1REF, from which OC1 is derived.

OC1REF is active high whereas OC1 active level depends on the CC1P bit.

000: Frozen - The comparison between the output compare register TIM1_CCR1 and the counter

register TIM1_CNT has no effect on the outputs.

001: Set channel 1 to active level on match - OC1REF signal is forced high when the counter

register TIM1_CNT matches the capture/compare register 1 (TIM1_CCR1).

010: Set channel 1 to inactive level on match - OC1REF signal is forced low when the counter

register TIM1_CNT matches the capture/compare register 1 (TIM1_CCR1).

011: Toggle - OC1REF toggles when TIM1_CNT = TIM1_CCR1

100: Force inactive level - OC1REF is forced low

101: Force active level - OC1REF is forced high

110: PWM mode 1 - In up-counting, channel 1 is active as long as TIM1_CNT < TIM1_CCR1,

otherwise, the channel is inactive. In down-counting, channel 1 is inactive (OC1REF = 0) as long as

TIM1_CNT > TIM1_CCR1, otherwise, the channel is active (OC1REF = 1).

111: PWM mode 2 - In up-counting, channel 1 is inactive as long as TIM1_CNT < TIM1_CCR1,

otherwise, the channel is active. In down-counting, channel 1 is active as long as TIM1_CNT >

TIM1_CCR1, otherwise, the channel is inactive.

Note: These bits can no longer be modified while LOCK level 3 has been programmed (LOCK bits in

TIM1_BKR register) and CC1S = 00 (the channel is configured in output).

In PWM mode 1 or 2, the OCiREF level changes only when the result of the comparison

changes or when the output compare mode switches from “frozen” mode to “PWM” mode (refer

to PWM mode on page 171 for more details).

On channels that have a complementary output, this bitfield is preloaded. If the CCPC bit is set

in the TIM1_CR2 register, the OCM active bits take the new value from the preload bits only

when a COM is generated.

Loading...

Loading...