RM0016 16-bit general purpose timers (TIM2, TIM3, TIM5)

Doc ID 14587 Rev 8 229/449

18.6.7 Event generation register (TIMx_EGR)

Address offset: 0x04 or 0x06 (TIM2), 0x04 (TIM3), 0x06 (TIM5); for TIM2 address see

Section

Reset value: 0x00

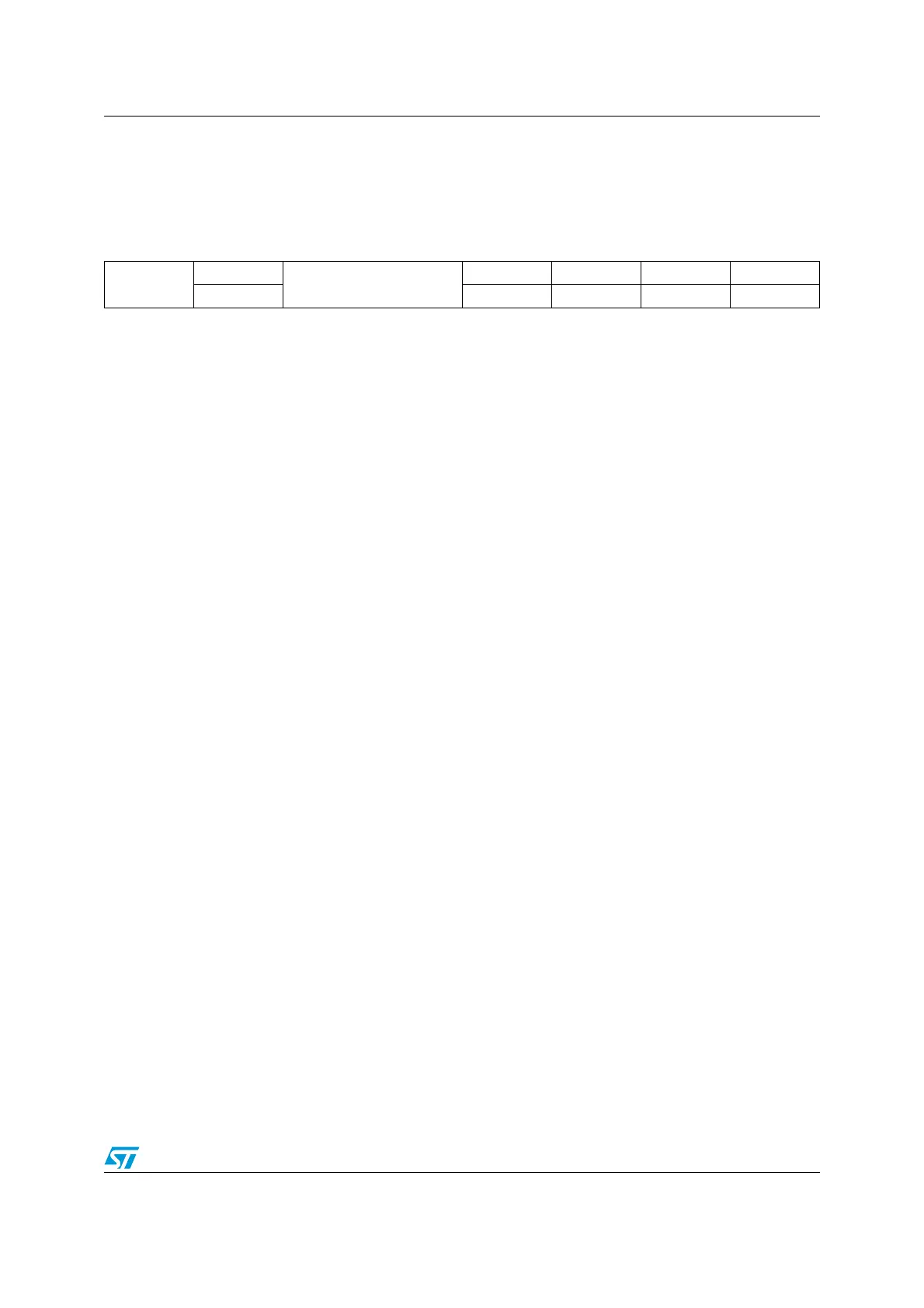

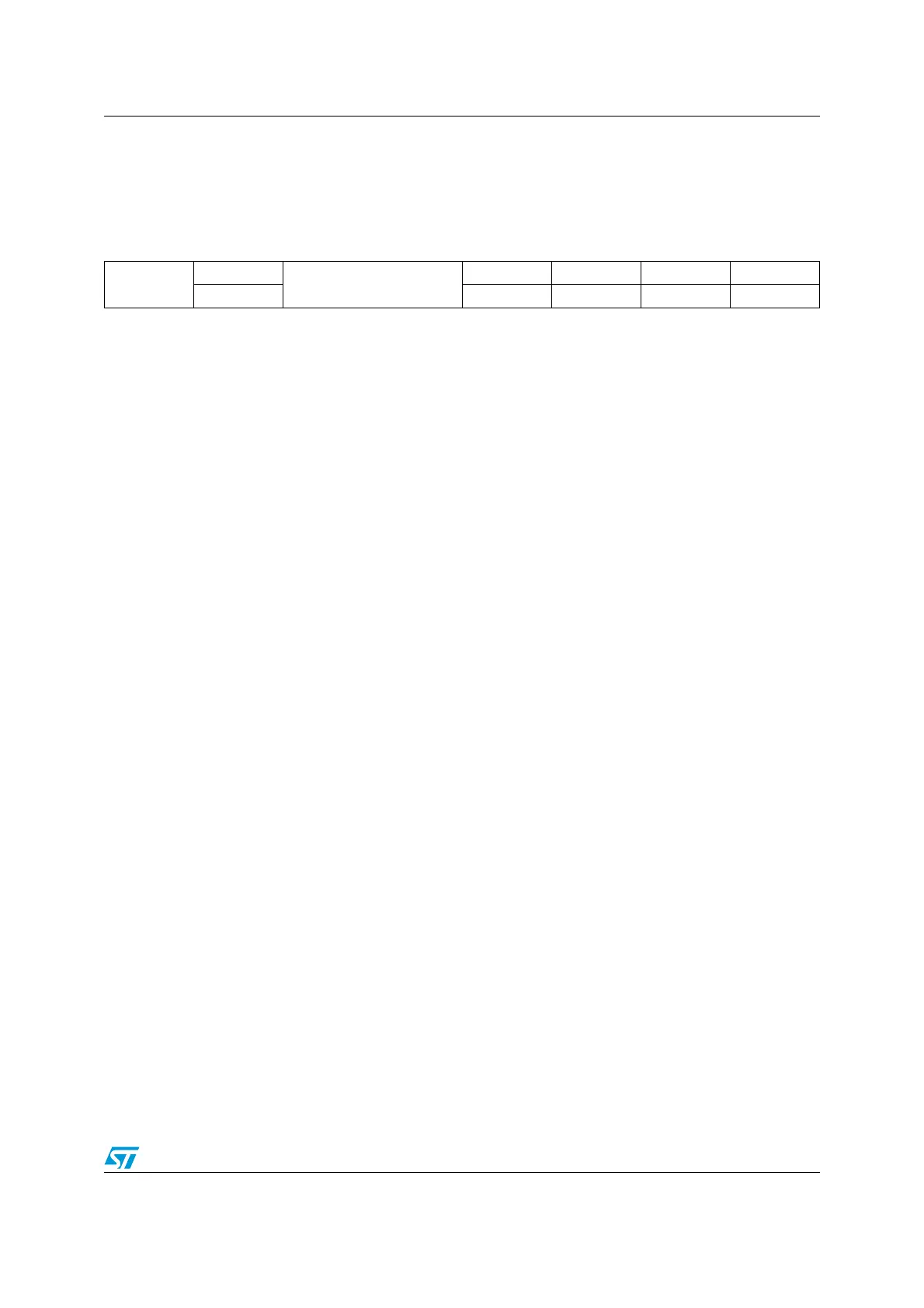

76543210

Reserved

TG

Reserved

CC3G

CC2G

CC1G UG

w

w

w

ww

Bit 7 Reserved

Bit 6 TG: Trigger generation

This bit is set by software to generate an event. It is automatically cleared by hardware.

0: No action

1: The TIF flag is set in TIM5_SR1 register. An interrupt is generated if enabled by the TIE bit

Note: In TIM2/TIM3 this bit is reserved.

Bits 5:4 Reserved

Bit 3 CC3G: Capture/compare 3 generation

Refer to CC1G description

Bit 2 CC2G: Capture/compare 2 generation

Refer to CC1G description

Bit 1 CC1G: Capture/compare 1 generation

This bit is set by software to generate an even. It is automatically cleared by hardware.

0: No action

1: A capture/compare event is generated on channel 1:

– If the CC1 channel is configured in output mode. In this case, the CC1IF flag is set, and the

corresponding interrupt request is sent if enabled.

– If the CC1 channel configured in input mode. In this case, the current value of the counter is

captured in the TIMx_CCR1 register. The CC1IF flag is set, and the corresponding interrupt request

is sent if enabled. The CC1OF flag is set if the CC1IF flag is already high.

Bit 0 UG: Update generation

This bit can be set by software, it is automatically cleared by hardware.

0: No action

1: Re-initializes the counter and generates an update of the registers. Note that the prescaler

counter is also cleared.

Loading...

Loading...