Serial peripheral interface (SPI) RM0016

266/449 Doc ID 14587 Rev 8

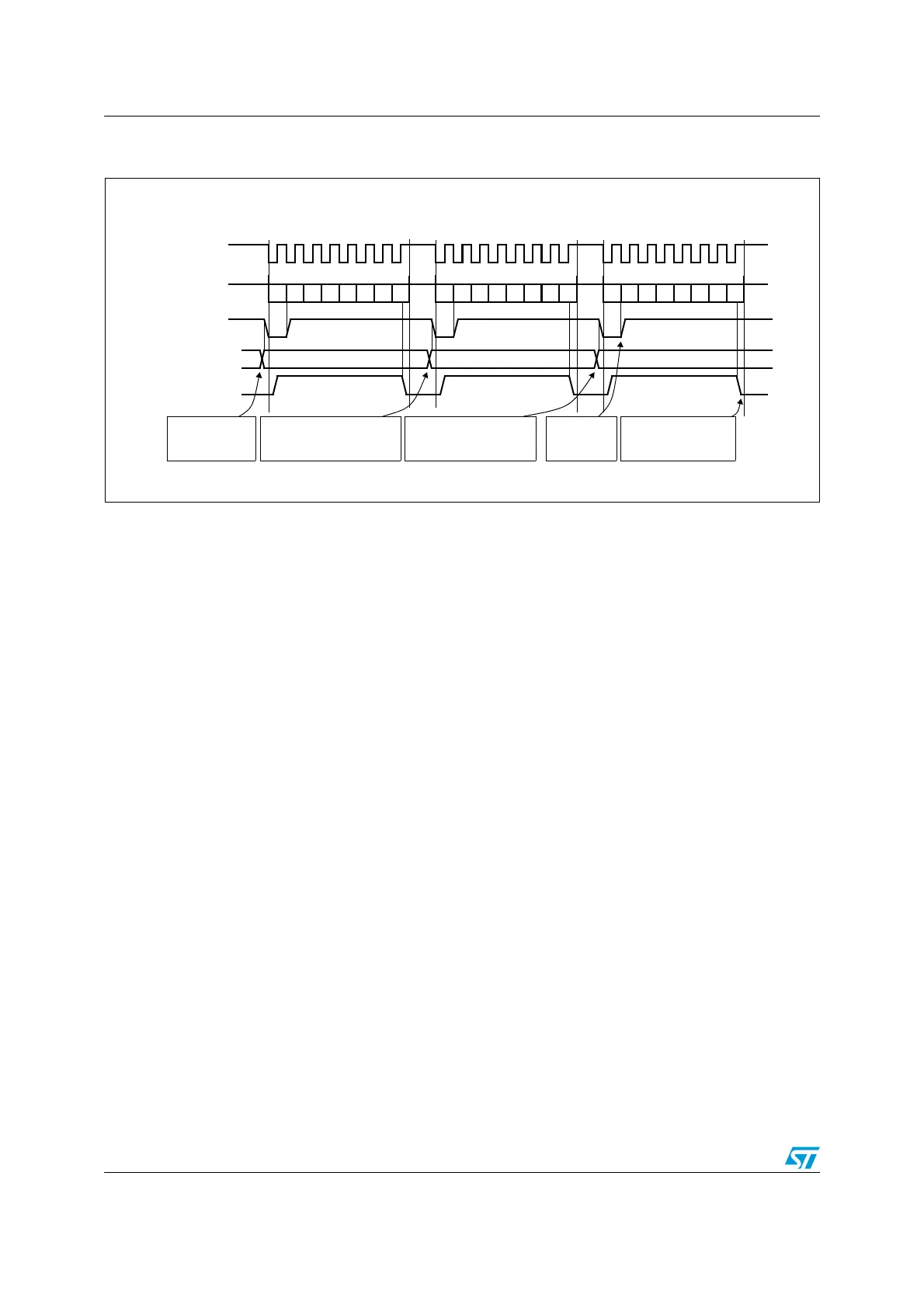

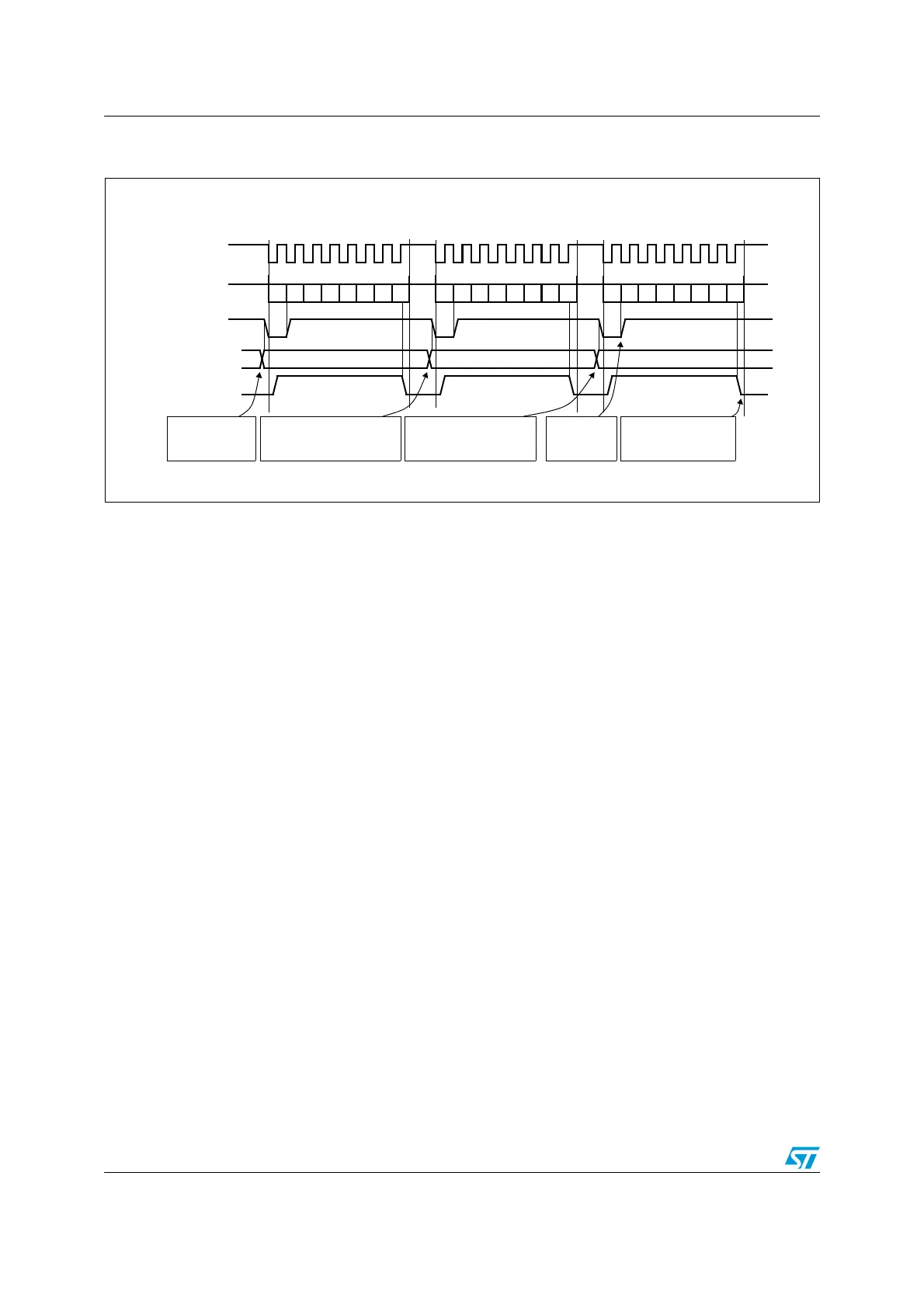

Figure 99. TXE/BSY behavior when transmitting (BDM = 0 and RXLONY = 0).

Case of discontinuous transfers

20.3.6 CRC calculation

A CRC calculator has been implemented for communication reliability. Separate CRC

calculators are implemented for transmitted data and received data. The CRC is calculated

using a programmable polynomial serially on each bit. The CRC is calculated on the

sampling clock edge defined by the CPHA and CPOL bits in the SPI_CR1 register.

CRC calculation is enabled by setting the CRCEN bit in the SPI_CR1 register. This action

resets the CRC registers (SPI_RXCRCR and SPI_TXCRCR). When the CRCNEXT bit in

SPI_CR2 is set, the SPI_TXCRCR value is transmitted at the end of the current byte

transmission.

If a byte is present in the Tx buffer, the CRC value is transmitted only after the transmission

of this byte. During the transmission of CRC, the CRC calculator is switched off and the

register value remains unchanged.

The CRCERR flag in the SPI_SR register is set if the value received in the shift register

during the SPI_TXCRCR value transmission does not match the SPI_RXCRCR value.

MOSI (out)

Tx buffer

DATA 1 = 0xF1

TXE flag

0xF1

BSY flag

0xF2

software writes 0xF1

into SPI_DR

software waits until TXE=1 but is

late to write 0xF2 into SPI_DR

software waits until TXE=1 but

is late to writes 0xF3 into

SPI_DR

SCK

DATA 2 = 0xF2 DATA 3 = 0xF3

Example with CPOL=1, CPHA = 1

0xF3

software waits

until TXE=1

software waits until BSY=0

(write SPI_DR)

b0 b1 b2 b3 b4 b5 b6 b7

b0 b1 b2 b3 b4 b5 b6 b7 b0 b1 b2 b3 b4 b5 b6 b7

Loading...

Loading...