Universal asynchronous receiver transmitter (UART) RM0016

316/449 Doc ID 14587 Rev 8

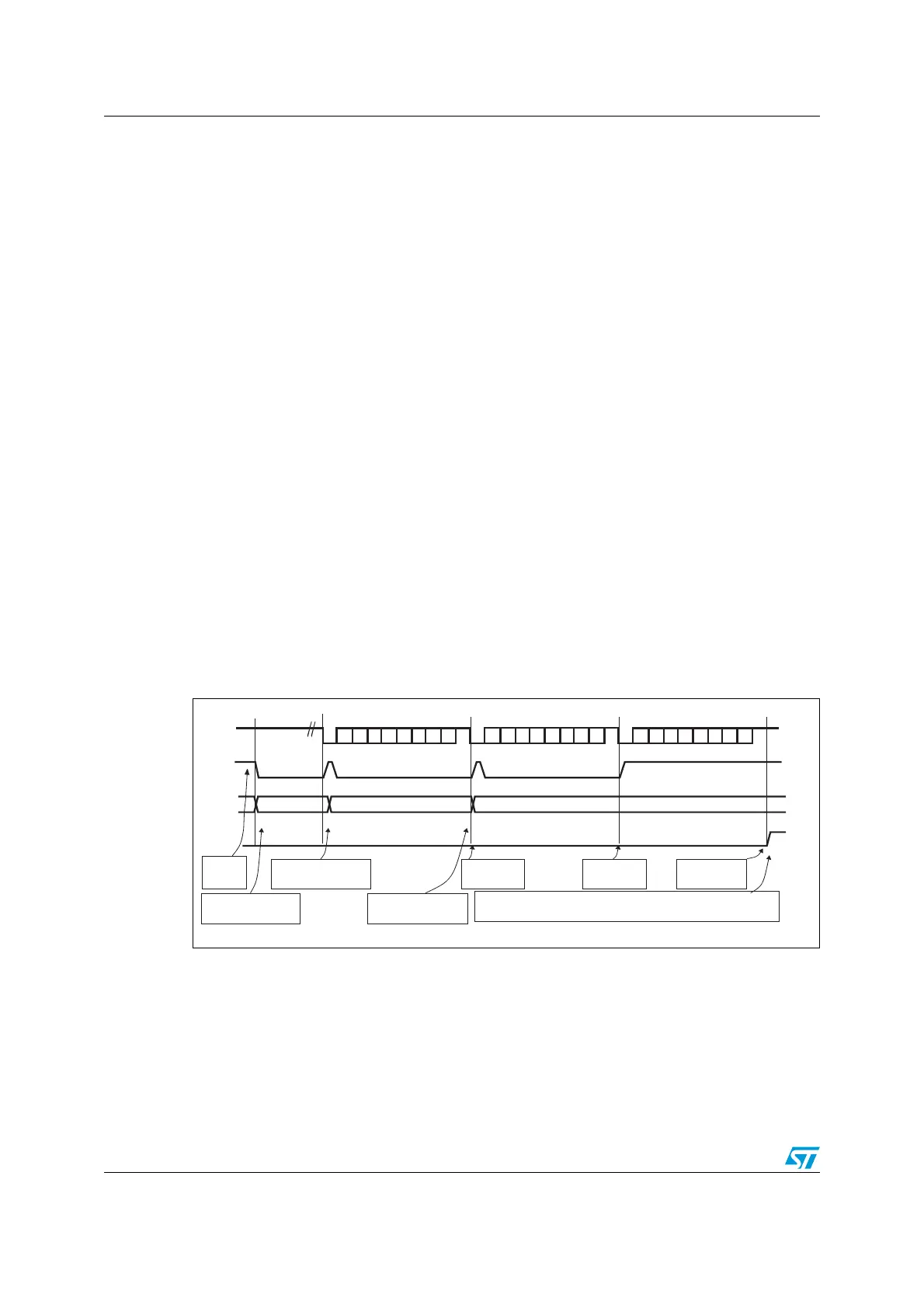

Single byte communication

Clearing the TXE bit is always performed by a write to the data register.

The TXE bit is set by hardware and it indicates:

● The data has been moved from TDR to the shift register and the data transmission has

started.

● The TDR register is empty.

● The next data can be written in the UART_DR register without overwriting the previous

data.

This flag generates an interrupt if the TIEN bit is set.

When a transmission is taking place, a write instruction to the UART_DR register stores the

data in the TDR register. The data is copied in the shift register at the end of the current

transmission.

When no transmission is taking place, a write instruction to the UART_DR register places

the data directly in the shift register, the data transmission starts, and the TXE bit is

immediately set.

If a frame transmission is complete (after the stop bit) and the TXE bit is set, the TC bit is

set. An interrupt is generated if the TCIEN is set in the UART_CR2 register. After writing the

last data in the UART_DR register, it is mandatory to wait until TC is set to ‘1’ before

entering Halt mode or disabling the UART (see Figure 115: TC/TXE behavior when

transmitting).

The following software sequence is required to clear the TC bit:

1. Read from the UART_SR register

2. Write to the UART_DR register

Figure 115. TC/TXE behavior when transmitting

1. This example assumes that several other transmissions occur after TE has been set.

Note: The TC bit can also be cleared by writing a ‘0’ to it. This clear sequence is recommended

only for multibuffer communication.

TX line

USART_DR

Frame 1

TXE flag

F2

TC flag

F3

Frame 2

Software waits until TXE = 1

and writes F2 into DR

Software waits until TXE = 1

and writes F3 into DR

TC is not set

because TXE = 0

Software waits until TC = 1

Frame 3

TC is set because

TXE = 1

Set by hardware and

cleared by software

Set by hardware and

cleared by software

Set by hardware

Set

Idle preamble

by hardware

F1

Software

enables the

USART

TC is not set

because TXE = 0

Software waits until TXE = 1

and writes F1 into DR

ai17121b

Loading...

Loading...