RM0016 16-bit advanced control timer (TIM1)

Doc ID 14587 Rev 8 139/449

17.3 TIM1 time base unit

The timer has a time base unit that includes:

● 16-bit up/down counter

● 16-bit auto-reload register

● Repetition counter

● Prescaler

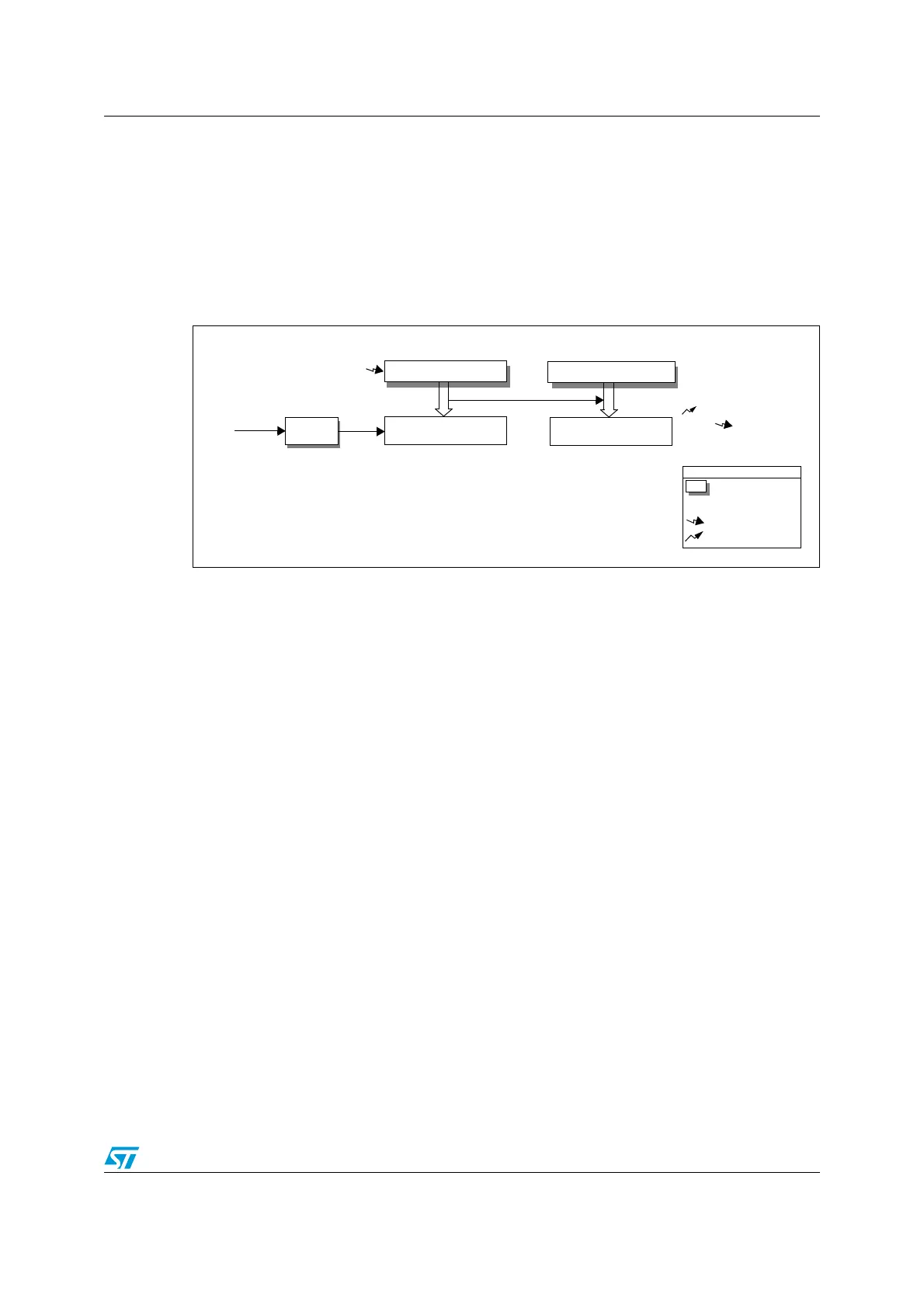

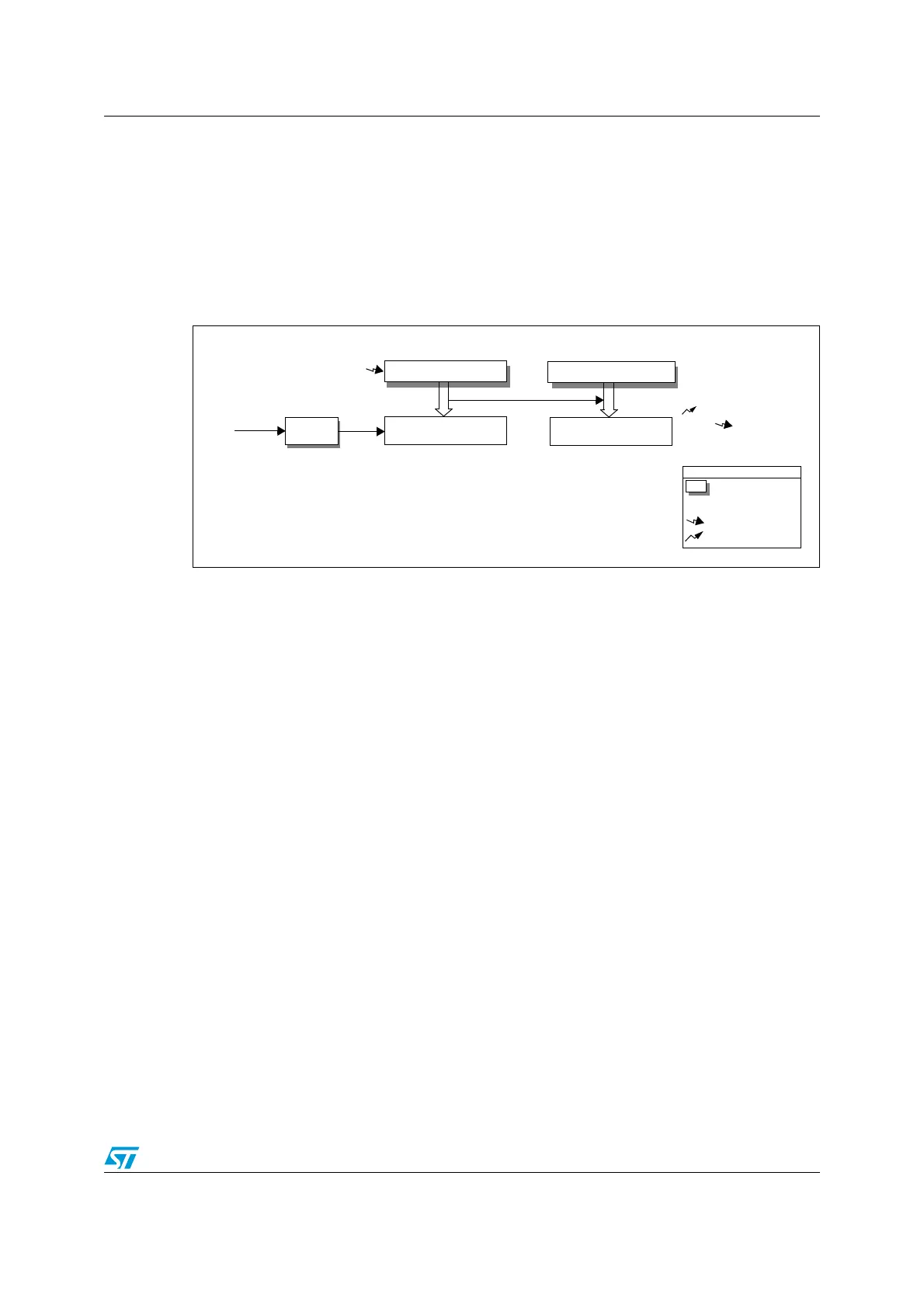

Figure 32. Time base unit

The 16-bit counter, the prescaler, the auto-reload register and the repetition counter register

can be written or read by software.

The auto-reload register is composed of a preload register plus a shadow register.

Writing to the auto-reload register can be done in two modes:

● Auto-reload preload enabled (ARPE bit set in the TIM1_CR1 register). In this mode,

when data is written to the auto-reload register, it is kept in the preload register and

transferred into the shadow register at the next update event (UEV).

● Auto-reload preload disabled (ARPE bit cleared in the TIM1_CR1 register). In this

mode, when data is written to the auto-reload register it is transferred into the shadow

register immediately.

An update event is generated:

● On a counter overflow or underflow

● By software, setting the UG bit in the TIM1_EGR register

● By a trigger event from the clock/trigger controller

With preload enabled (ARPE = 1), when an update event occurs: The auto-reload shadow

register is updated with the preload value (TIM1_ARR) and the buffer of the prescaler is

reloaded with the preload value (content of the TIM1_PSCR register).

The UEV can be disabled by setting the UDIS bit in the TIM1_CR1

The counter is clocked by the prescaler output CK_CNT, which is enabled only when the

counter enable bit (CEN) in TIM1_CR1 register is set.

Note: The actual counter enable signal CNT_EN is set 1 clock cycle after CEN.

Prescaler

Auto-reload register

16-bit Counter

CK_PSC

CK_CNT

TIM1_PSCRH, PSCRL TIM1_CNTRH, CNTRL

TIM1_ARRH,

ARRL

UEV

UIF

UEV

Repetition counter register

Repetition Counter

TIM1_RCR

Reg

event

Legend:

Preload registers transferred

to shadow registers on update

control bit

interrupt

event (

UEV)

according to

Loading...

Loading...