RM0016 Inter-integrated circuit (I

2

C) interface

Doc ID 14587 Rev 8 305/449

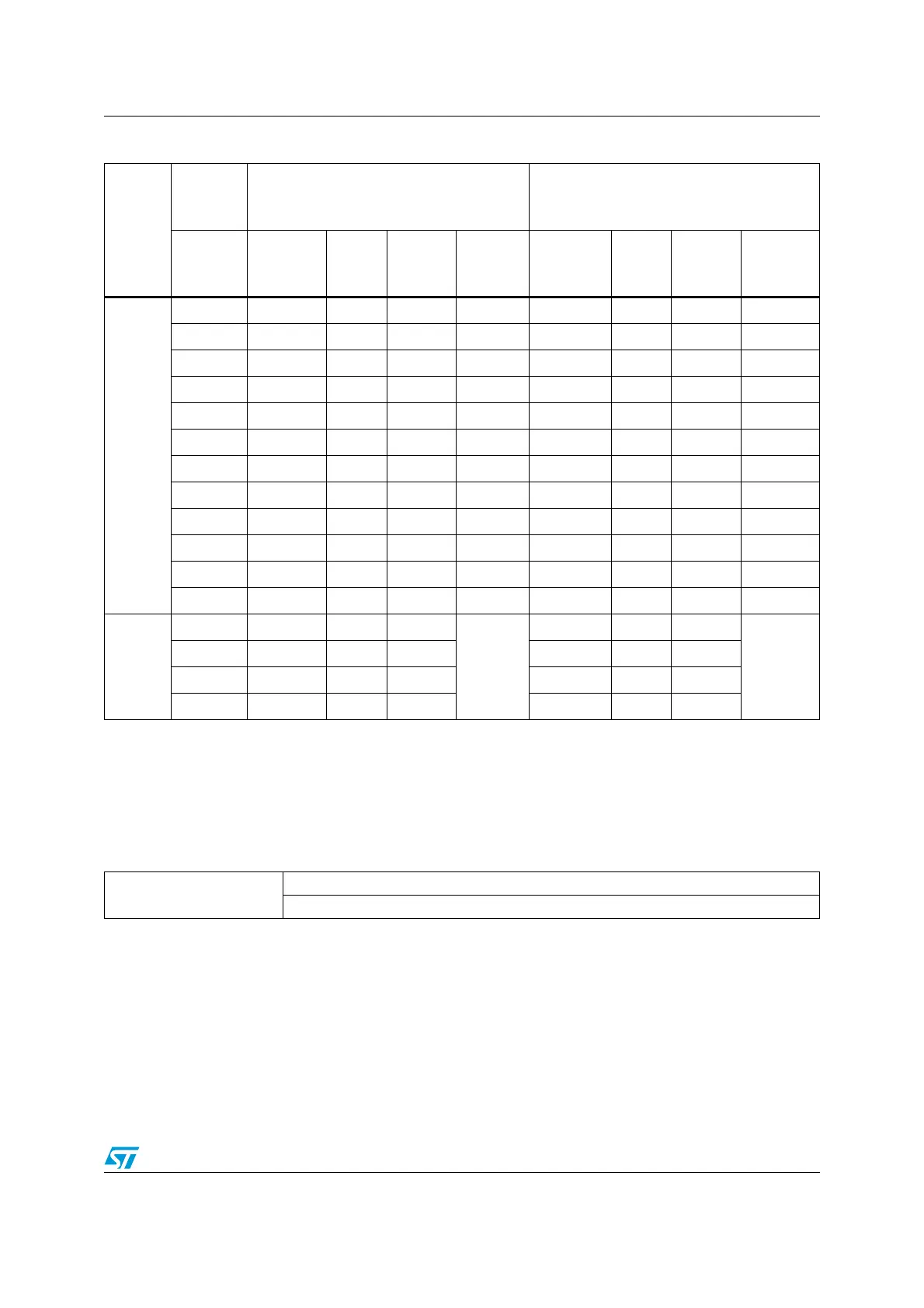

21.7.13 TRISE register (I2C_TRISER)

Address offset: 0x0D

Reset value: 0x02

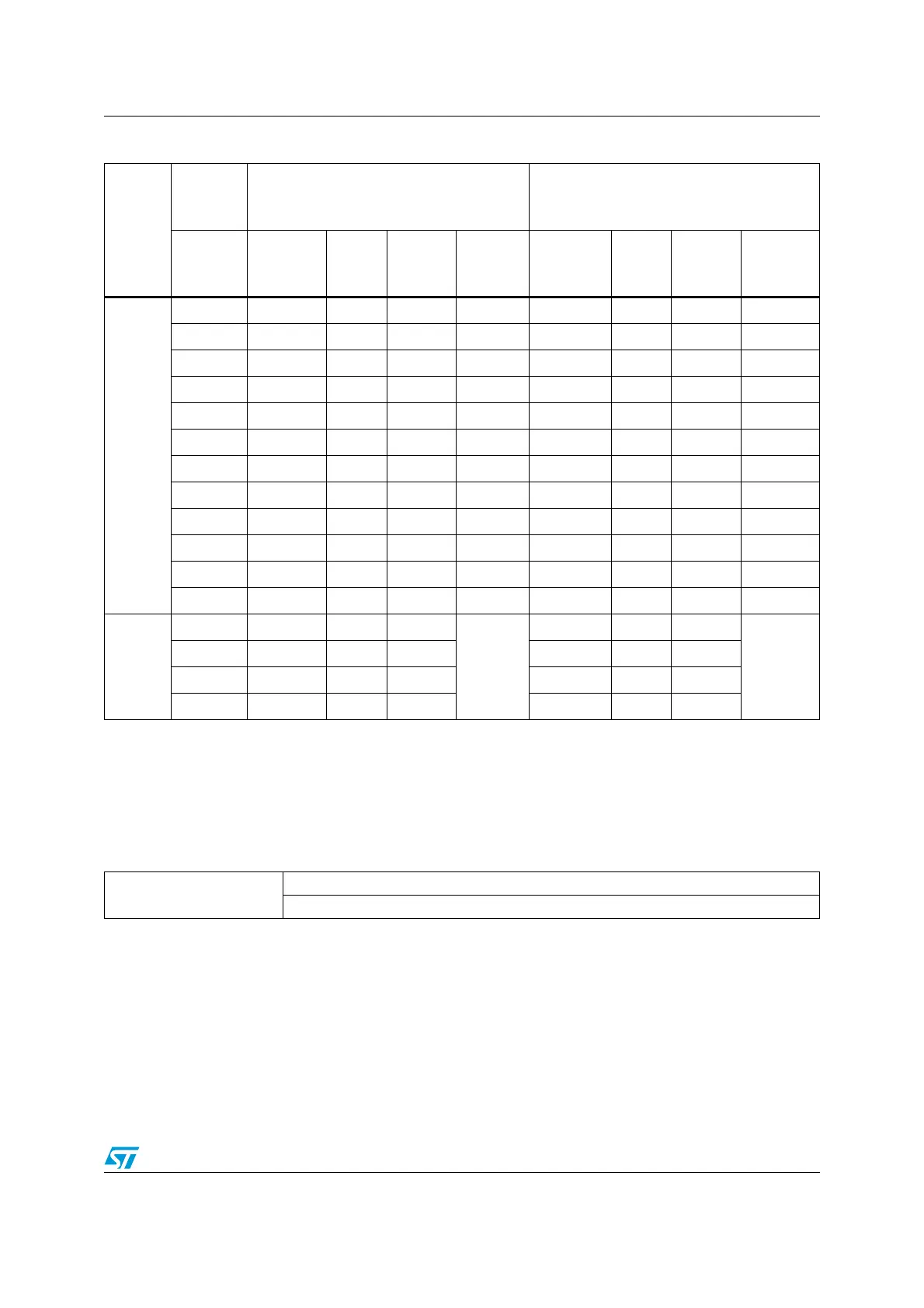

Table 50. I2C_CCR values for SCL frequency table (f

MASTER

= 10 MHz or 16 MHz

(1)

)

1. The following table gives the values to be written in the I2C_CCR register to obtain the required I²C SCL line frequency

I2C

Speed

I2C

frequency

(f

SCL

)

f

MASTER

= 10 MHz f

MASTER

= 16 MHz

in Hz

Actual

(Hz)

% Error

(%)

I2C_CCR

(h)

Duty

cycle

bit

Actual

(Hz)

% Error

(%)

I2C_CCR

(h)

Duty cycle

bit

Fast

speed

400000 400000 0 1 1 410256.41 2.56 D 0

370000 370370.37 0.10 9 0 380952.38 2.96 E 0

350000 370370.37 5.82 9 0 355555.56 1.59 F 0

320000 333333.33 4.17 A 0 320000 0 2 1

300000 303030.30 1.01 B 0 313725.49 4.57 11 0

270000 277777.78 2.88 C 0 280701.75 3.96 13 0

250000 256410.26 2.56 D 0 253968.25 1.59 15 0

220000 222222.22 1.01 F 0 222222.22 1.01 18 0

200000 200000 0 2 1 205128.20 2.56 1A 0

170000 175438.60 3.20 13 0 172043.01 1.20 1F 0

150000 151515.15 1.01 16 0 152380.95 1.59 23 0

120000 123456.79 2.88 1B 0 121212.12 1.01 2C 0

Standard

speed

100000 100000 0 32

No impact

100000 0 50

No impact

50000 50000 0 64 50000 0 A0

30000 30120.48 0.40 A6 30075.19 0.25 10A

20000 20000 0 FA 20000 0 190

76543210

Reserved

TRISE[5:0]

rw

Bits 7:6 Reserved

Loading...

Loading...