Timer overview RM0016

134/449 Doc ID 14587 Rev 8

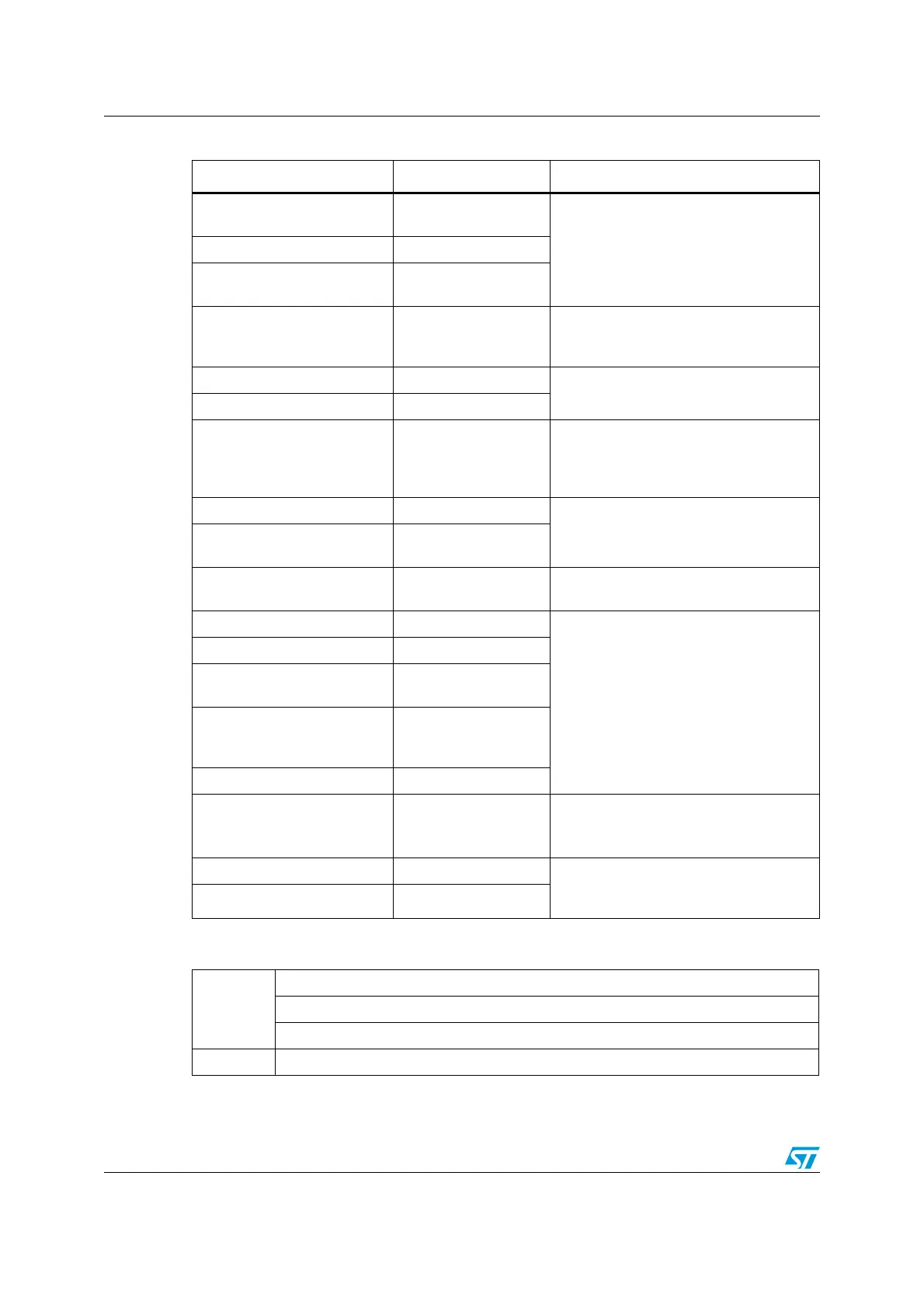

ETR

External trigger from

TIMx_ETR pin

Figure 47: External trigger input block

diagram on page 152

ETRF External trigger filtered

ETRP

External trigger

prescaled

f

MASTER

Timer peripheral clock

from clock controller

(CLK)

ICi : IC1, IC2 Input capture

Figure 64: Input stage of TIM 1 channel 1

on page 165

ICiPS: IC1PS, IC2PS Input capture prescaled

MATCH1 Compare match

Figure 54: Trigger/master mode selection

blocks on page 158 and Section 17.7.2:

Control register 2 (TIM1_CR2) on

page 187

OCi: OC1, OC2 Timer output channel

Figure 68: Detailed output stage of

channel with complementary output

(channel 1) on page 169

OCiREF: OC1REF, OC2REF

Output compare

reference signal

TGI Trigger interrupt

Figure 43: Clock/trigger controller block

diagram on page 149

TIi : TI1, TI2 Timer input

Figure 64: Input stage of TIM 1 channel 1

on page 165

TIiF: TI1F, TI2F Timer input filtered

TI1_ED

Timer input edge

detector

TIiFPn: TI1FP1, TI1FP2,

TI2FP1, TI2FP2, TI3FP3,

TI3FP4, TI4FP3, TI4FP4

Timer input filtered

prescaled

TRC Trigger capture

TRGI

Trigger input to

clock/trigger/slave

mode controller

Figure 44: Control circuit in normal mode,

fCK_PSC = fMASTER on page 150

UEV Update event Figure 35: Counter update when ARPE =

0 (ARR not preloaded) with prescaler = 2

on page 142

UIF Update interrupt

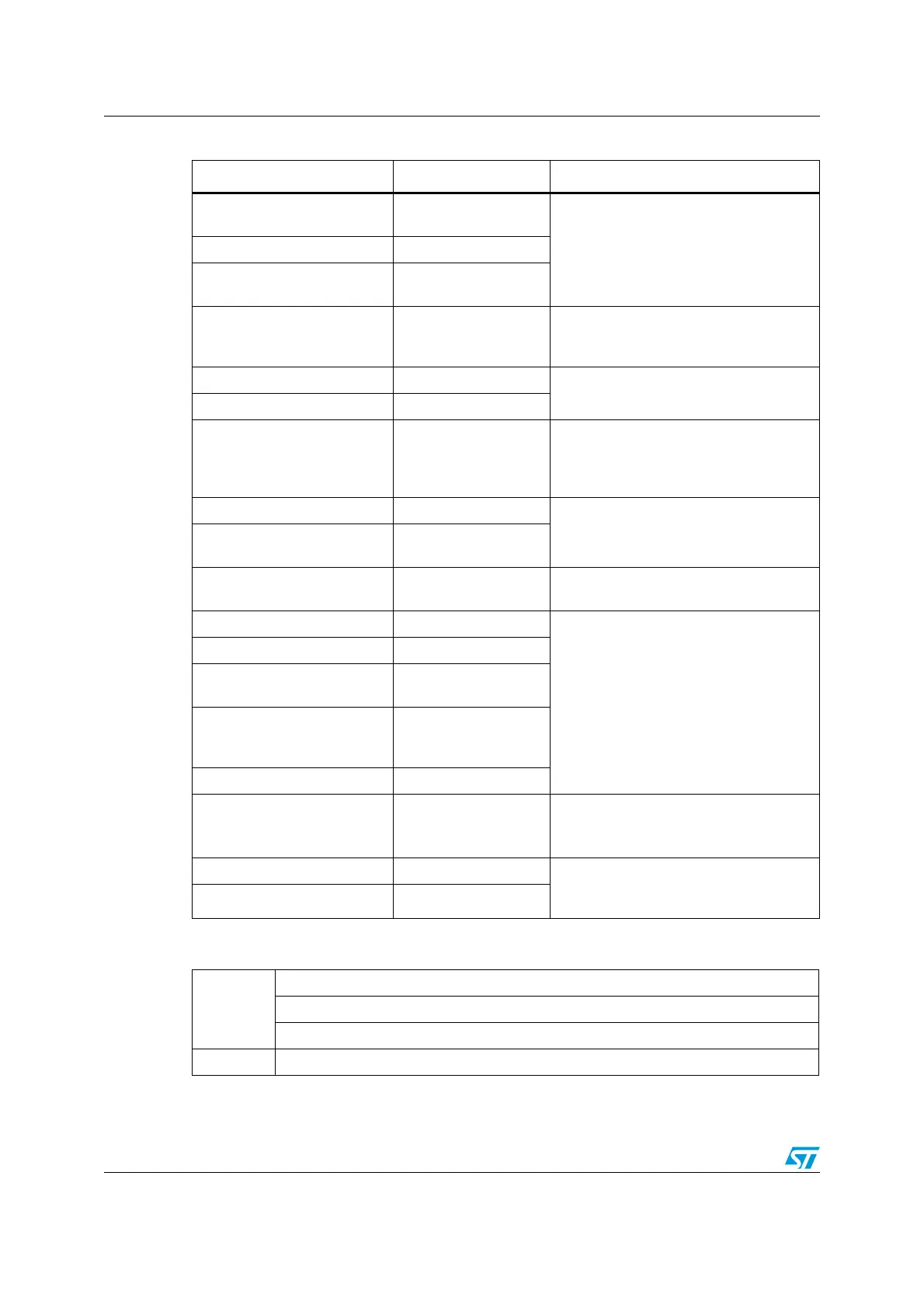

Table 36. Explanation of indices‘i’, ‘n’, and ‘x’

(1)

i

Signal number: May be 1, 2, 3, 4 depending on the device

Bit number: May be 1, 2, 3, 4 ........ depending on the device

Register number: May be 1, 2, 3, 4 depending on the device

n Signal number (when i is already used): May be 1, 2, 3, 4 depending on the device

Table 35. Glossary of internal timer signals (continued)

Internal signal name Description Related figures

Loading...

Loading...