RM0016 Universal asynchronous receiver transmitter (UART)

Doc ID 14587 Rev 8 329/449

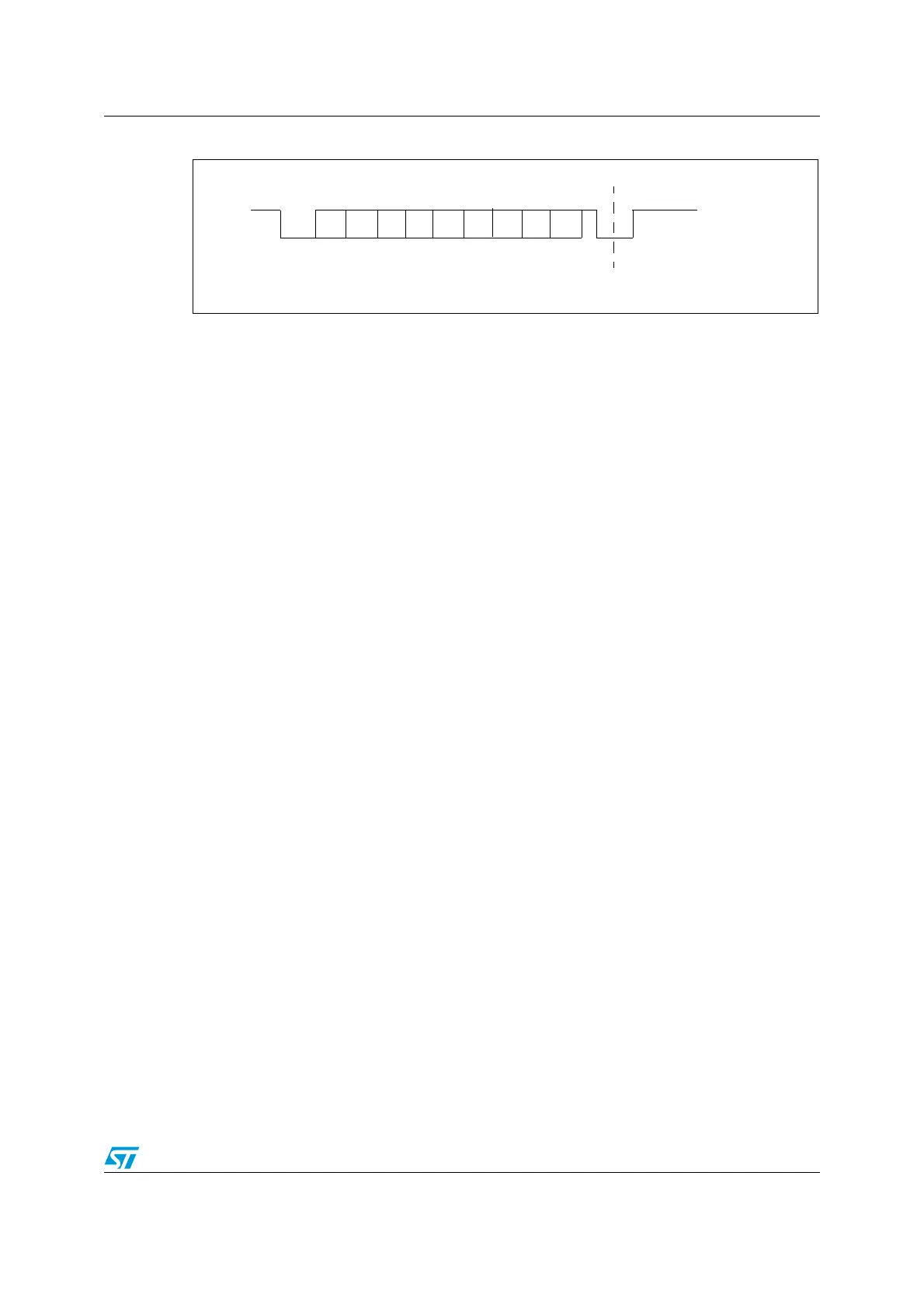

Figure 125. ISO 7816-3 asynchronous protocol

When connected to a smartcard, the UART_TX output drives a bidirectional line that is also

driven by the smartcard.

Smartcard is a single wire half duplex communication protocol.

● Transmission of data from the transmit shift register is guaranteed to be delayed by a

minimum of 1/2 baud clock. In normal operation a full transmit shift register will start

shifting on the next baud clock edge. In Smartcard mode this transmission is further

delayed by a guaranteed 1/2 baud clock.

● If a parity error is detected during reception of a frame programmed with a 1.5 stop bit

period, the transmit line is pulled low for a baud clock period after 1/2 baud clock

period. This is to indicate to the Smartcard that the data transmitted to the UART has

not been correctly received. This NACK signal (pulling transmit line low for 1 baud

clock) will cause a framing error on the transmitter side (configured with 1.5 stop bits).

The application can handle re-sending of data according to the protocol. A parity error

is ‘NACK’ed by the receiver if the NACK control bit is set, otherwise a NACK is not

transmitted.

● The TE bit must be set to enable:

– Data transmission

– Transmission of acknowledgements in case of parity error.

Software must manage the timing of data transmission to avoid conflicts on the

data line when it writes new data in the data register.

● The RE bit must be set to enable:

– Data reception (sent by the Smartcard as well as by the UART),

– Detection of acknowledgements in case of parity error.

● The assertion of the TC flag can be delayed by programming the Guard Time register.

In normal operation, TC is asserted when the transmit shift register is empty and no

further transmit requests are outstanding. In Smartcard mode an empty transmit shift

register triggers the guard time counter to count up to the programmed value in the

Guard Time register. TC is forced low during this time. When the guard time counter

reaches the programmed value TC is asserted high.

● The de-assertion of TC flag is unaffected by Smartcard mode.

● If a framing error is detected on the transmitter end (due to a NACK from the receiver),

the NACK will not be detected as a start bit by the receive block of the transmitter.

According to the ISO protocol, the duration of the received NACK can be 1 or 2 baud

clock periods.

● On the receiver side, if a parity error is detected and a NACK is transmitted the receiver

will not detect the NACK as a start bit.

S

0

1

23

5

4

67

P

Start

bit

Line pulled low

by receiver during stop in

case of parity error

Guard time

Loading...

Loading...