Serial peripheral interface (SPI) RM0016

262/449 Doc ID 14587 Rev 8

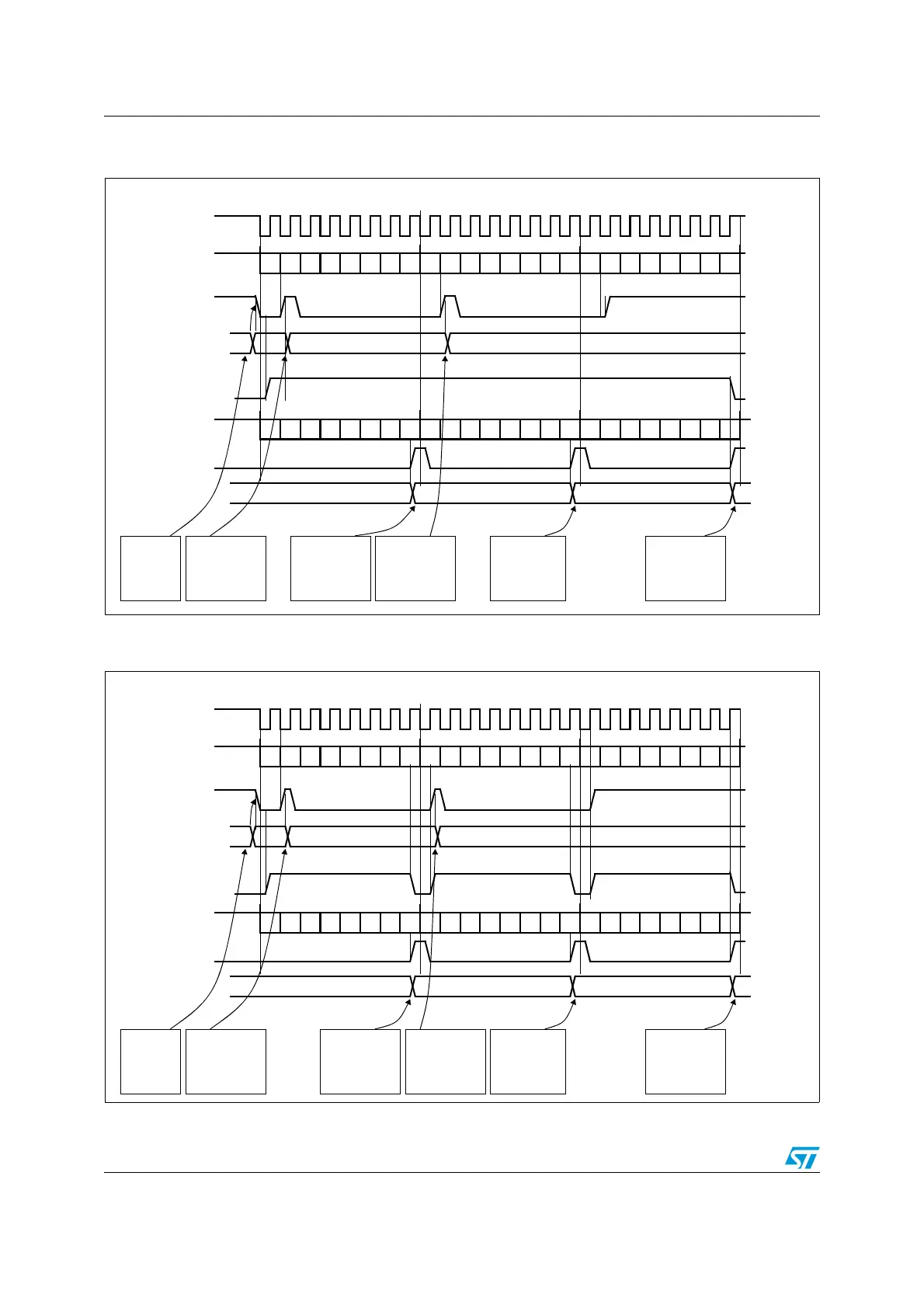

Figure 94. TXE/RXNE/BSY behavior in full duplex mode (RXONLY = 0).

Case of continuous transfers

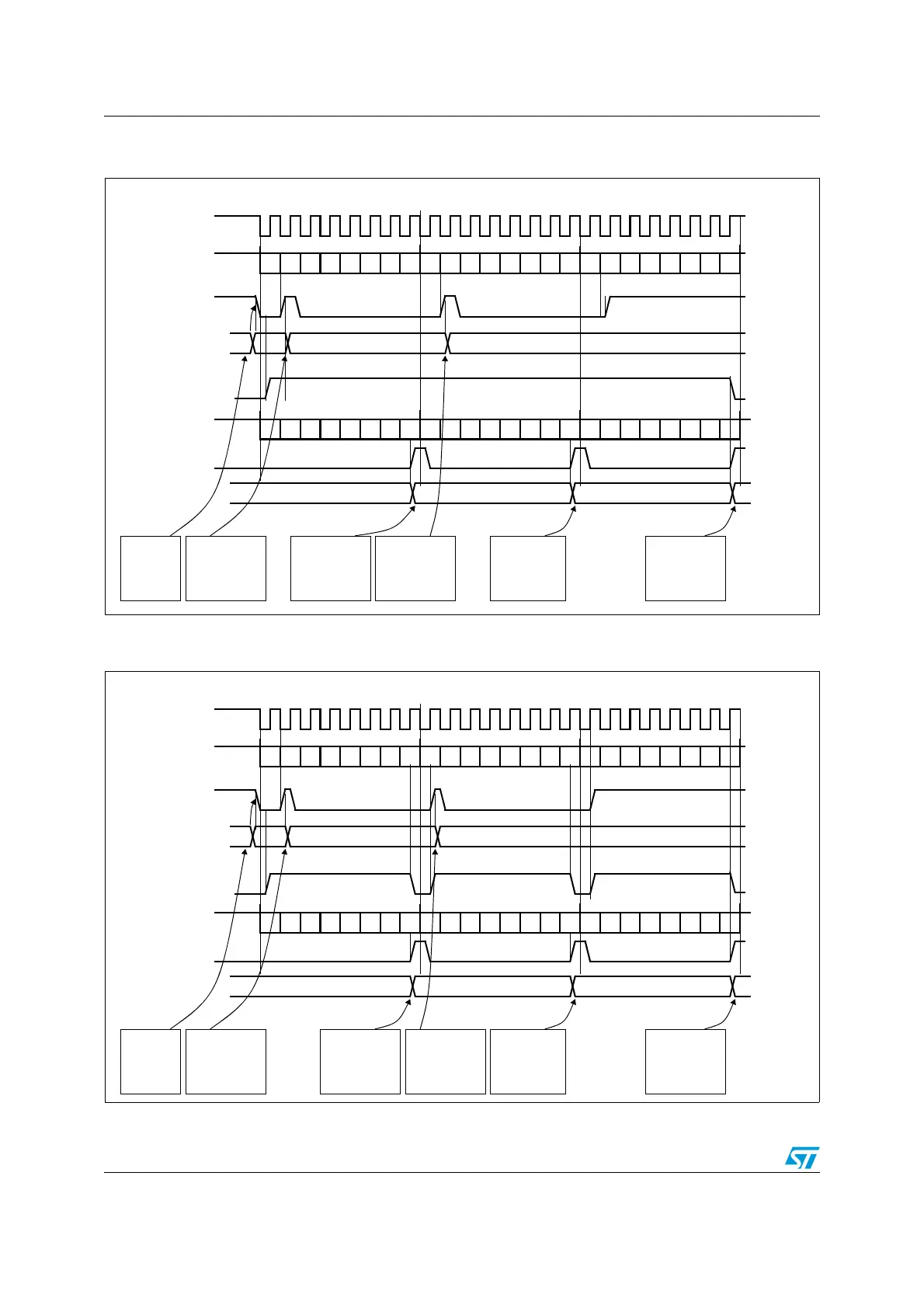

Figure 95. TXE/RXNE/BSY behavior in slave / full duplex mode

(BDM = 0, RXONLY = 0). Case of continuous transfers

MISO/MOSI (in)

Tx Buffer

DATA1 = 0xA1

TXE flag

0xF2

BSY flag

0xF3

software

writes 0xF1 in

SPI_DR

software waits until

TXE=1 and writes

0xF2 in SPI_DR

software waits until

RXNE=1 and reads

0xA1 from SPI_DR

set by hw

cleared by sw

set by hw

cleared by sw

set by hw

set by hw

SCK

DATA 2 = 0xA2

DATA 3 = 0xA3

reset by hw

Example in Master Mode with CPOL=1, CPHA=1

0xF1

RXNE flag

(write SPI_DR)

Rx Buffer

set by hw cleared by sw

MISO/MOSI (out)

DATA1 = 0xF1

DATA2 = 0xF2

DATA3 = 0xF3

(read SPI_DR)

0xA1

0xA2 0xA3

software waits until

TXE=1 and writes

0xF3 in SPI_DR

software waits un-

til RXNE=1 and

reads 0xA2 from

SPI_ DR

software waits until

RXNE=1 and reads

0xA3 from SPI_DR

b0 b1 b2 b3 b4 b5 b6 b7 b0 b1 b2 b3 b4 b5 b6 b7 b0 b1 b2 b3 b4 b5 b6 b7

b0 b1 b2 b3 b4 b5 b6 b7 b0 b1 b2 b3 b4 b5 b6 b7 b0 b1 b2 b3 b4 b5 b6 b7

0xF1

set by hw

MISO/MOSI (in)

Tx Buffer

DATA 1 = 0xA1

TXE flag

0xF2

BSY flag

0xF3

software

writes 0xF1 in

SPI_DR

software waits until

TXE=1 and writes

0xF2 in SPI_DR

software waits until

RXNE=1 and reads

0xA1 from SPI_DR

set by hw

cleared by sw

set by hw

cleared by sw

set by hw

SCK

DATA 2 = 0xA2

DATA 3 = 0xA3

reset by hw

Example in Slave Mode with CPOL=1, CPHA=1

RXNE flag

(write SPI_DR)

Rx Buffer

set by hw cleared by sw

MISO/MOSI (out)

DATA 1 = 0xF1 DATA 2 = 0xF2

DATA 3 = 0xF3

(read SPI_DR)

0xA1

0xA2 0xA3

software waits until

TXE=1 and writes

0xF3 in SPI_DR

software waits un-

til RXNE=1 and

reads 0xA2 from

SPI_ DR

software waits until

RXNE=1 and reads

0xA3 from SPI_DR

b0 b1 b2 b3 b4 b5 b6 b7 b0 b1 b2 b3 b4 b5 b6 b7 b0 b1 b2 b3 b4 b5 b6 b7

b0 b1 b2 b3 b4 b5 b6 b7 b0 b1 b2 b3 b4 b5 b6 b7 b0 b1 b2 b3 b4 b5 b6 b7

Loading...

Loading...