Universal asynchronous receiver transmitter (UART) RM0016

352/449 Doc ID 14587 Rev 8

22.7.6 Control register 2 (UART_CR2)

Address offset: 0x05

Reset value: 0x00

Bit 2 PCEN: Parity control enable.

–UART Mode

This bit selects the hardware parity control (generation and detection). When the parity control is

enabled, the computed parity is inserted at the MSB position (9th bit if M=1; 8th bit if M=0) and parity

is checked on the received data. This bit is set and cleared by software. Once it is set, PCEN is

active after the current byte (in reception and in transmission).

0: Parity control disabled

1: Parity control enabled

– LIN slave mode

This bit enables the LIN identifier parity check while the UART is in LIN slave mode.

0: Identifier parity check disabled

1: Identifier parity check enabled

Bit 1 PS: Parity selection.

This bit selects the odd or even parity when the parity generation/detection is enabled (PCEN bit set)

in UART mode. It is set and cleared by software. The parity will be selected after the current byte.

0: Even parity

1: Odd parity

Bit 0 PIEN: Parity interrupt enable.

This bit is set and cleared by software.

0: Parity interrupt disabled

1: Parity interrupt is generated whenever PE=1 in the UART_SR register

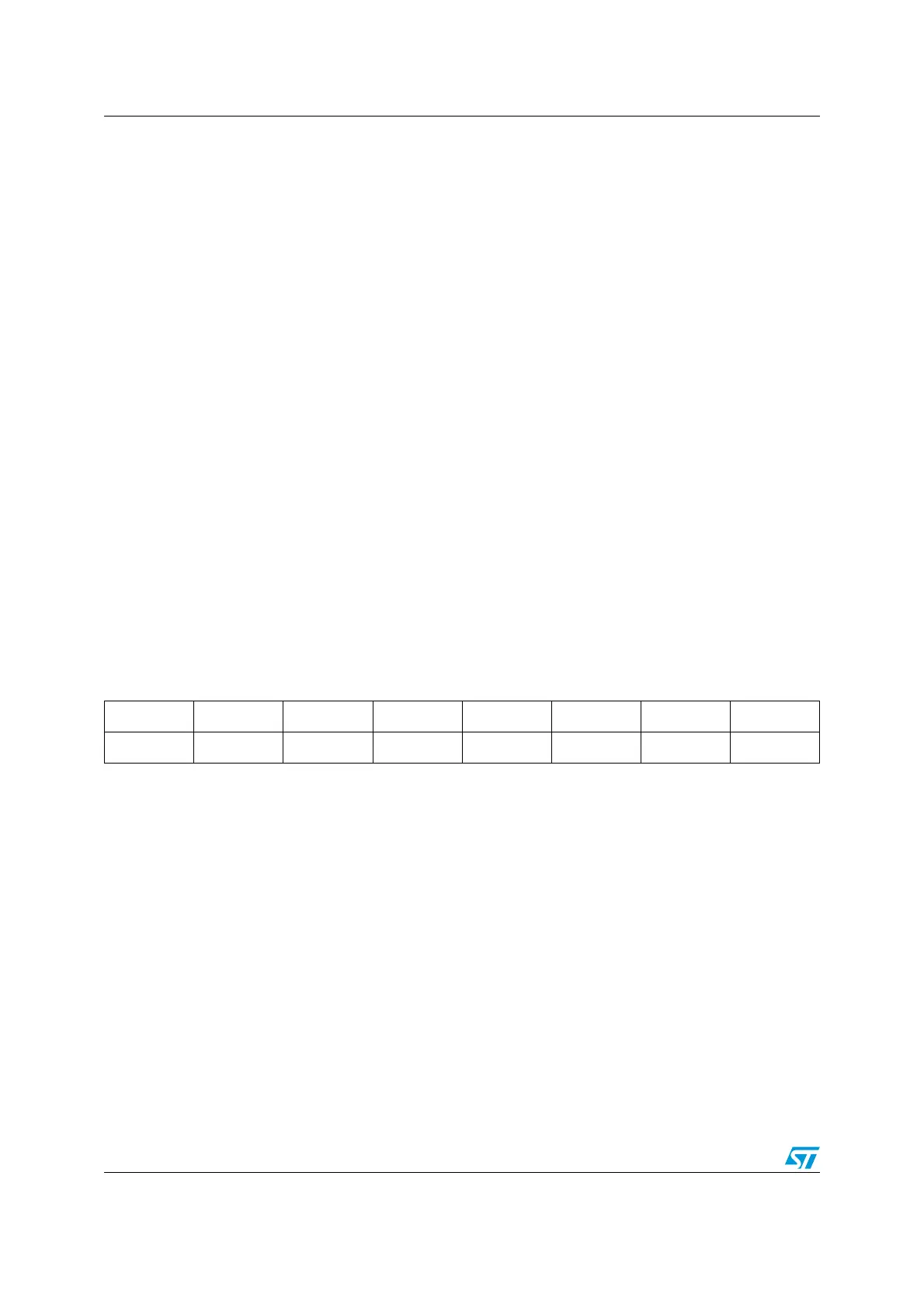

76543210

TIEN TCIEN RIEN ILIEN TEN REN RWU SBK

rw rw rw rw rw rw rw rw

Bit 7 TIEN: Transmitter interrupt enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An UART interrupt is generated whenever TXE=1 in the UART_SR register

Bit 6 TCIEN: Transmission complete interrupt enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An UART interrupt is generated whenever TC=1 in the UART_SR register

Bit 5 RIEN: Receiver interrupt enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An UART interrupt is generated whenever OR=1 or RXNE=1 in the UART_SR register

Bit 4 ILIEN: IDLE Line interrupt enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An UART interrupt is generated whenever IDLE=1 in the UART_SR register

Loading...

Loading...