RM0016 16-bit advanced control timer (TIM1)

Doc ID 14587 Rev 8 181/449

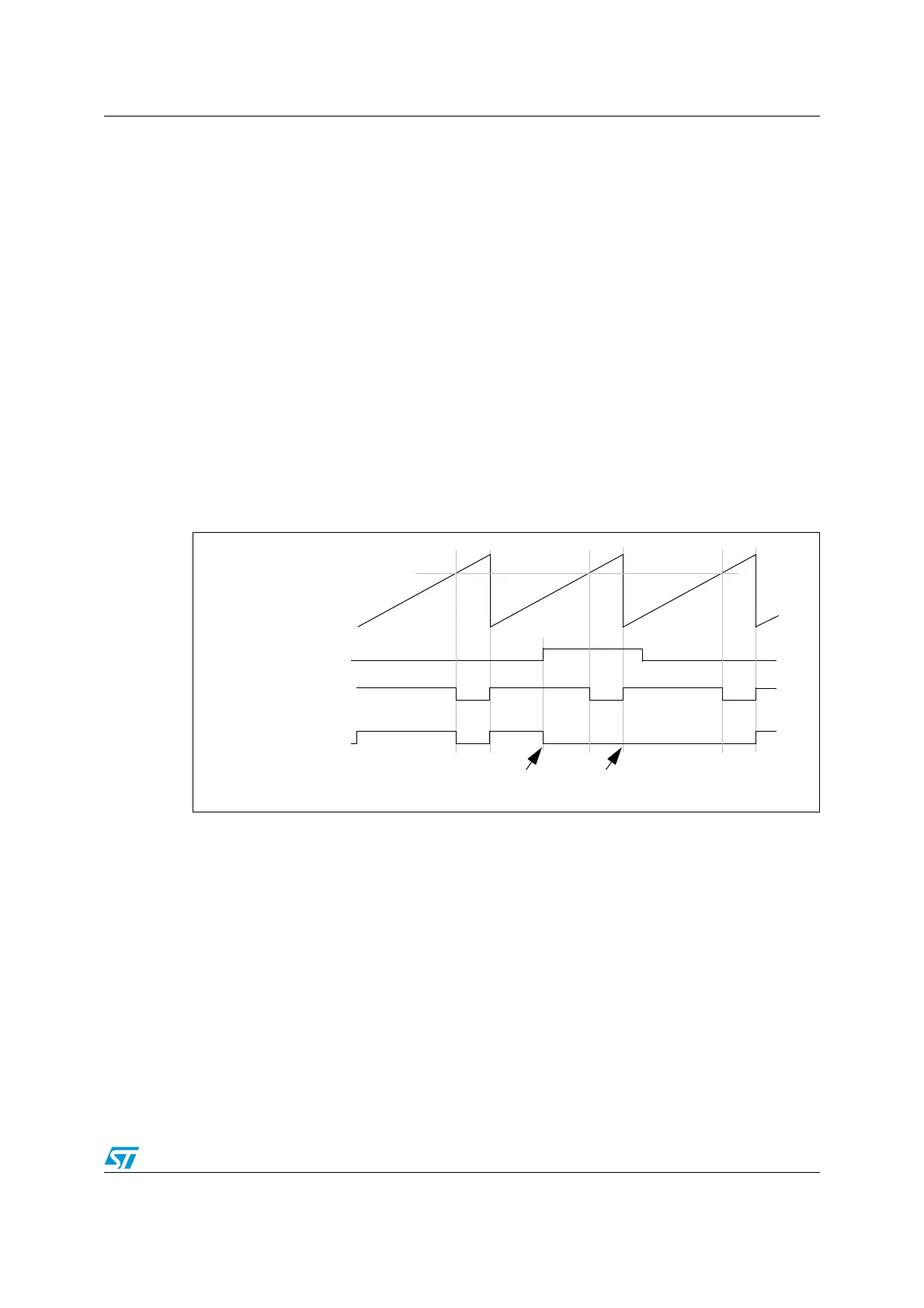

17.5.9 Clearing the OCiREF signal on an external event

The OCiREF signal of a given channel can be cleared when a high level is detected on

ETRF (if OCiCE =1 in the TIM1_CCMRi registers, one enable bit per channel). The OCiREF

signal remains low until the next UEV occurs. This function can be used in output compare

mode and PWM mode only. It does not work in forced mode.

The OCiREF signal can be connected to the output of a comparator and be used for current

handling by configuring the external trigger as follows:

1. Switch off the external trigger prescaler by setting bits ETPS[1:0] in the TIM1_ETR

register to 00.

2. Disable external clock mode 2 by setting the ECE bit in the TIM1_ETR register to 0

3. Configure the external trigger polarity (ETP) and the external trigger filter (ETF) as

desired.

Refer to Figure 47: External trigger input block diagram.

Figure 79 shows the behavior of the OCiREF signal when the ETRF input becomes high, for

both values of the enable bits OCiCE. In this example, the timer is programmed in PWM

mode.

Figure 79. ETR activation

OCiREF

counter (CNT)

OCiREF

ETRF

(OCiCE=0)

(OCiCE=1)

ETRF

becomes high

ETRF

still high

(CCRx)

Loading...

Loading...