RM0016 Controller area network (beCAN)

Doc ID 14587 Rev 8 393/449

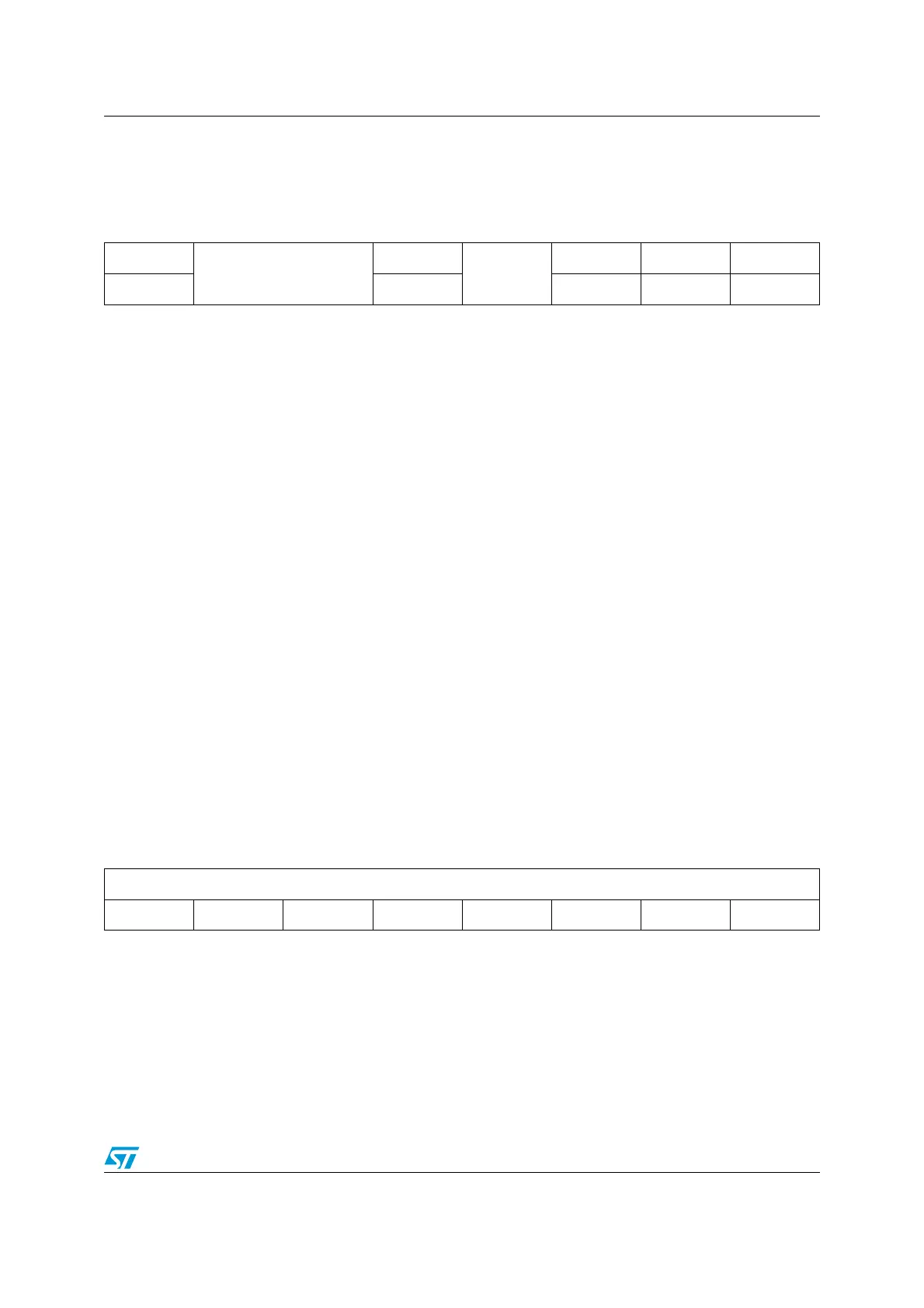

23.11.10 CAN error interrupt enable register (CAN_EIER)

Address offset: See Table 70.

Reset value: 0000 0000 (00h)

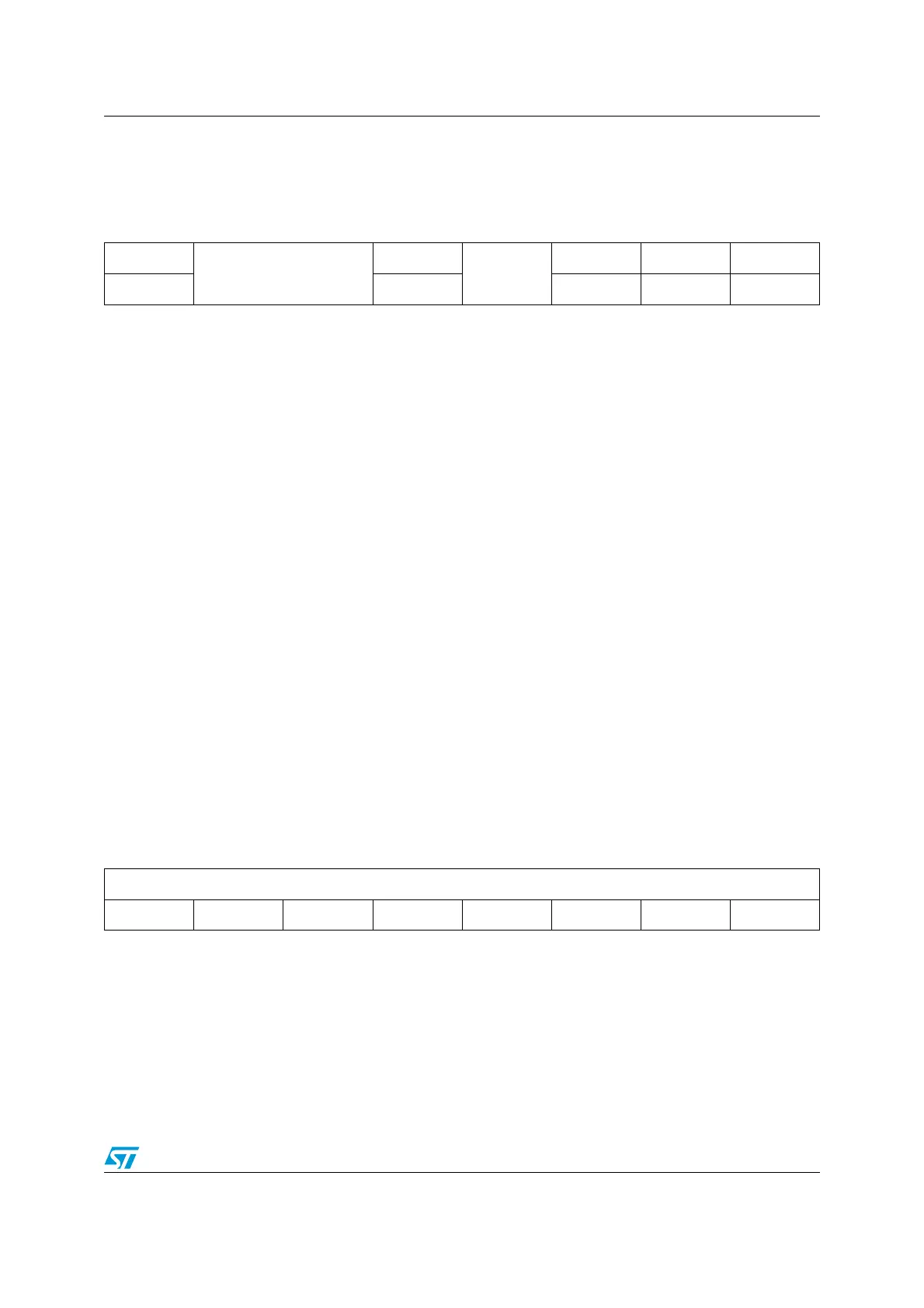

23.11.11 CAN transmit error counter register (CAN_TECR)

Address offset: See Table 70.

Reset value: 0000 0000 (00h)

76543210

ERRIE

Reserved

LECIE

Reserved

BOFIE EPVIE EWGIE

rw rw rw rw rw

Bit 7 ERRIE Error interrupt enable

0: No interrupt is generated when an error condition is pending in the CAN_ESR (ERRI bit in

CAN_MSR is set).

1: An interrupt is generated when an error condition is pending in the CAN_ESR (ERRI bit in

CAN_MSR is set).

Refer to Figure 155 for more details.

Bit 6:5 Reserved.

Bit 4 LECIE Last error code interrupt enable

0: ERRI bit is not set when the error code in LEC[2:0] is set by hardware on error detection.

1: ERRI bit is set when the error code in LEC[2:0] is set by hardware on error detection.

Bit 3 Reserved.

Bit 2 BOFIE Bus-Off interrupt enable

0: ERRI bit is not set when BOFF is set.

1: ERRI bit is set when BOFF is set.

Bit 1 EPVIE Error passive interrupt enable

0: ERRI bit is not set when EPVF is set.

1: ERRI bit is set when EPVF is set.

Bit 0 EWGIE Error warning interrupt enable

0: ERRI bit is not set when EWGF is set.

1: ERRI bit is set when EWGF is set.

76543210

TEC[7:0]

rrrrrrrr

Bits 7:0 TEC[7:0] Transmit error counter

In case of an error during transmission, this counter is incremented by 8 depending on the error

condition as defined by the CAN standard. After every successful transmission the counter is

decremented by 1 or reset to 0 if the CAN controller exited from bus-off to error active state. When

the counter value exceeds 127, the CAN controller enters the error passive state. When the counter

value exceeds 255, the CAN controller enters the bus-off state.

Loading...

Loading...