RM0016 Inter-integrated circuit (I

2

C) interface

Doc ID 14587 Rev 8 301/449

21.7.9 Status register 3 (I2C_SR3)

Address offset: 0x09

Reset value: 0x00

Bit 1 ARLO: Arbitration lost (master mode)

0: No Arbitration lost detected

1: Arbitration lost detected

Set by hardware when the interface loses the arbitration of the bus to another master.

– Cleared by software writing 0, or by hardware when PE=0.

After an ARLO event the interface switches back automatically to Slave mode (MSL=0).

Bit 0 BERR: Bus error

0: No misplaced Start or Stop condition

1: Misplaced Start or Stop condition

– Set by hardware when the interface detects a SDA rising or falling edge while SCL is high,

occuring in a non-valid position during a byte transfer.

– Cleared by software writing 0, or by hardware when PE=0.

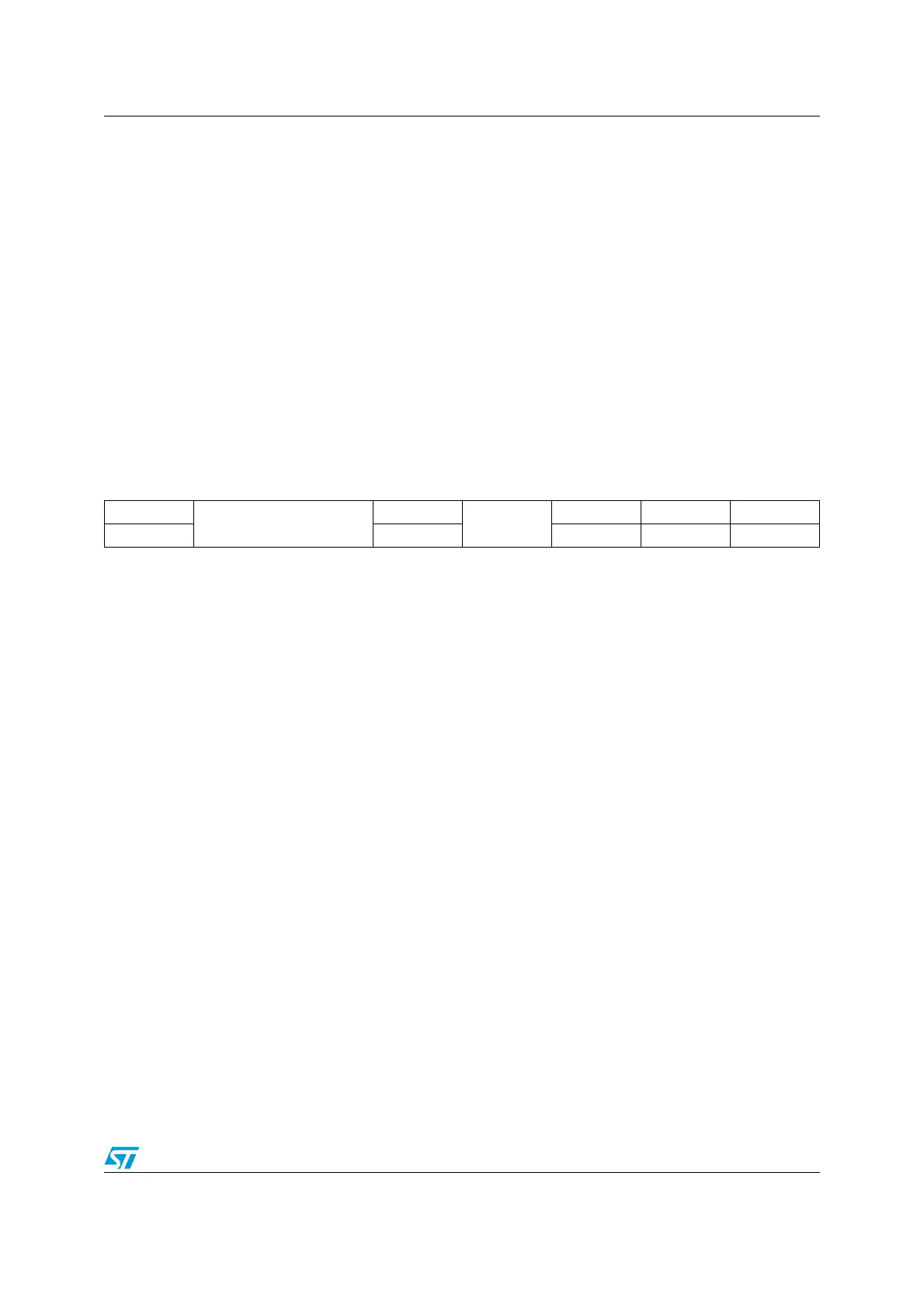

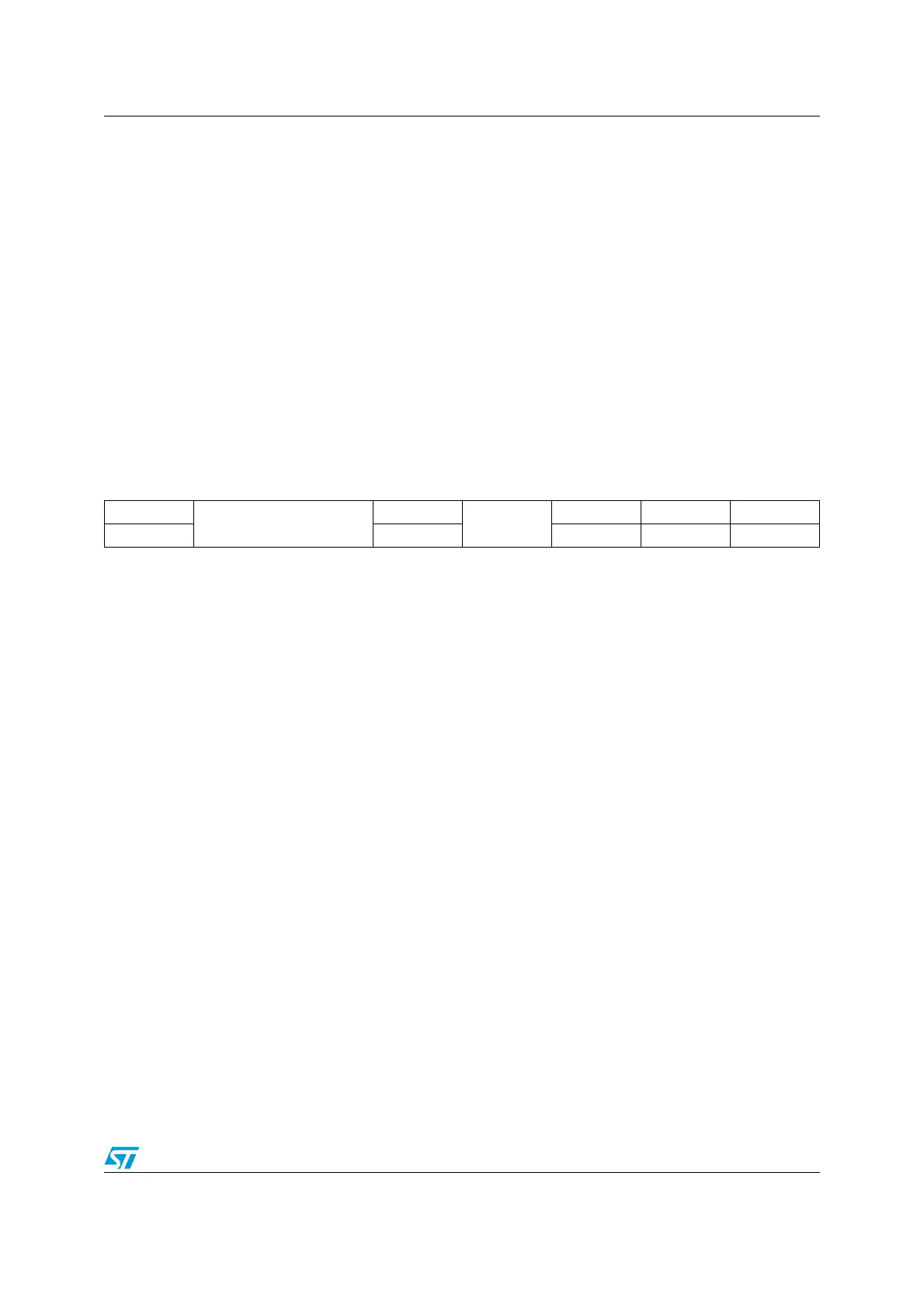

76543210

DUALF

Reserved

GENCALL

Reserved

TRA BUSY MSL

rrrrr

Bits 7:5 Reserved.

Bit 4 GENCALL: General call header (Slave mode)

0: No general call

1: General call header received when ENGC=1

– Cleared by hardware after a Stop condition or repeated Start condition, or when PE=0.

Bit 3 Reserved

Bit 2 TRA: Transmitter/Receiver

0: Data bytes received

1: Data bytes transmitted

This bit is set depending on R/W bit of address byte, at the end of total address phase.

It is also cleared by hardware after detection of Stop condition (STOPF=1), repeated Start condition,

loss of bus arbitration (ARLO=1), or when PE=0.

Bit 1 BUSY: Bus busy

0: No communication on the bus

1: Communication ongoing on the bus

– Set by hardware on detection of SDA or SCL low

– cleared by hardware on detection of a Stop condition.

It indicates a communication in progress on the bus. This information is still updated when the

interface is disabled (PE=0).

Bit 0 MSL: Master/Slave

0: Slave mode

1: Master mode

– Set by hardware as soon as the interface is in Master mode (SB=1).

– Cleared by hardware after detecting a Stop condition on the bus or a loss of arbitration

(ARLO=1), or by hardware when PE=0.

Loading...

Loading...