16-bit advanced control timer (TIM1) RM0016

206/449 Doc ID 14587 Rev 8

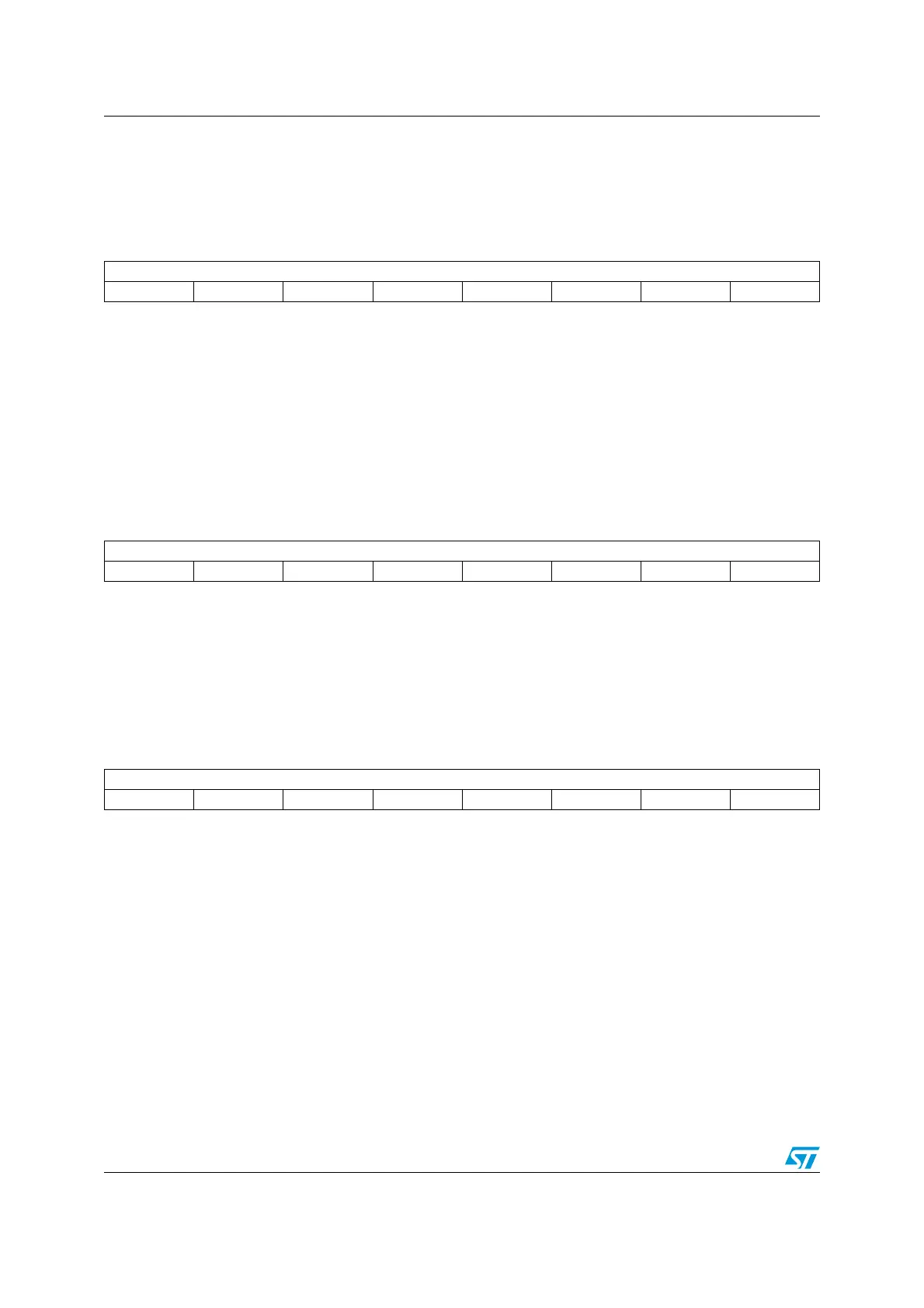

17.7.19 Auto-reload register high (TIM1_ARRH)

Address offset: 0x12

Reset value: 0xFF

17.7.20 Auto-reload register low (TIM1_ARRL)

Address offset: 0x13

Reset value: 0xFF

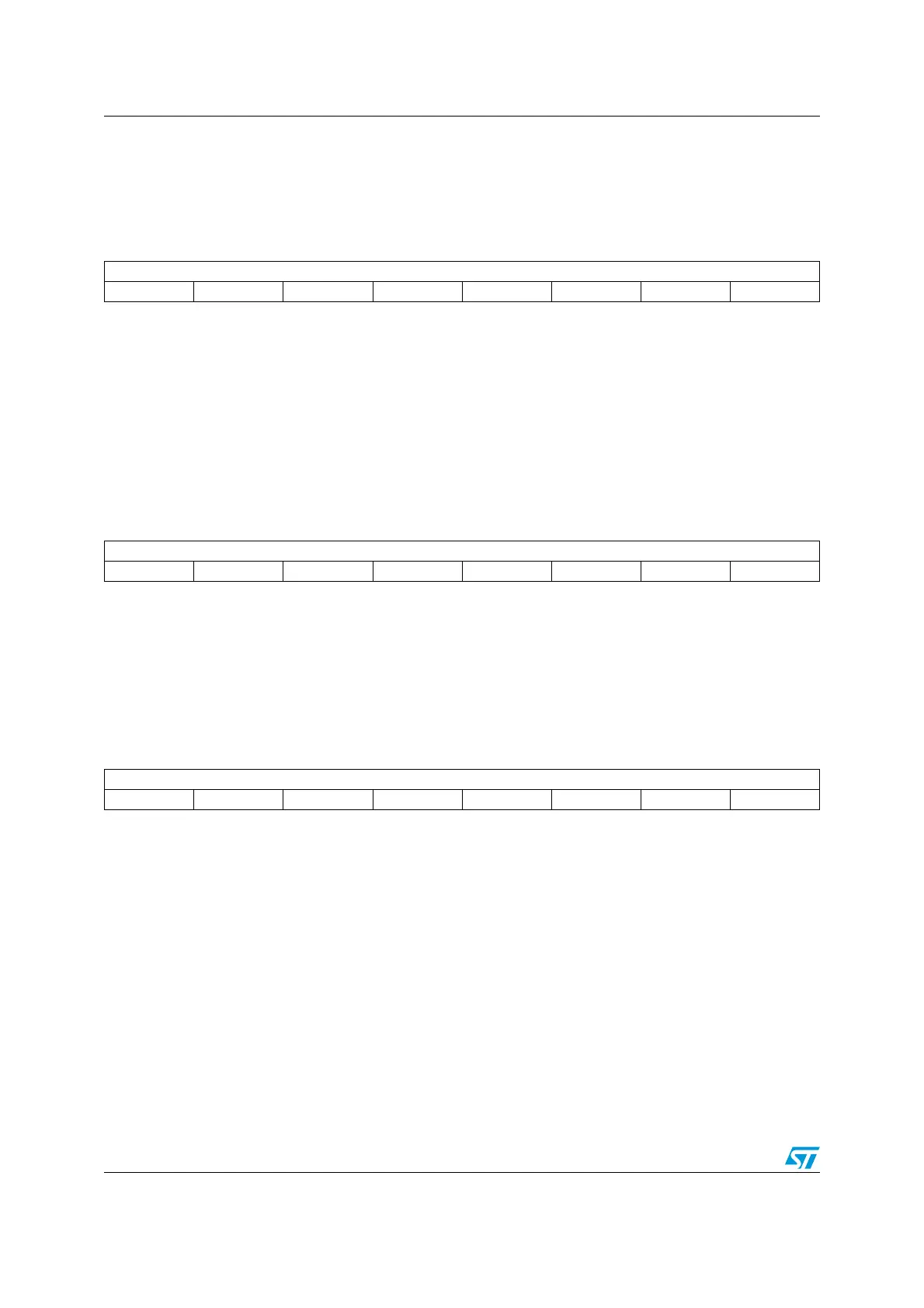

17.7.21 Repetition counter register (TIM1_RCR)

Address offset: 0x14

Reset value: 0x00

76543210

ARR[15:8]

rw rw rw rw rw rw rw rw

Bits 7:0 ARR[15:8]: Auto-reload value (MSB)

ARR is the value to be loaded in the actual auto-reload register. Refer to the Section 17.3: TIM1 time

base unit on page 139 for more details about ARR update and behavior. The counter is blocked

while the auto-reload value is null.

76543210

ARR[7:0]

rw rw rw rw rw rw rw rw

Bits 7:0 ARR[7:0]: Auto-reload value (LSB).

76543210

REP[7:0]

rw rw rw rw rw rw rw rw

Bits 7:0 REP[7:0]: Repetition counter value.

When the preload registers are enabled, these bits allow the user to set up the update rate of the

compare registers (periodic transfers from preload to shadow registers) as well as the update

interrupt generation rate if the update interrupt is enabled (UIE=1).

Each time the REP_CNT related down-counter reaches zero, a UEV is generated and it restarts

counting from the REP value. As REP_CNT is reloaded with the REP value only at the repetition

update event U_RC, any write to the TIM1_RCR register is not taken into account until the next

repetition update event.

In PWM mode (REP+1) corresponds to:

– The number of PWM periods in edge-aligned mode

– The number of half PWM periods in center-aligned mode

Loading...

Loading...